# Radiation hard electronics for HEP experiments: problems and solutions

Federico Faccio CERN / EP-ESE-ME

### Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

### **Application Specific Integrated Circuits (ASICs)**

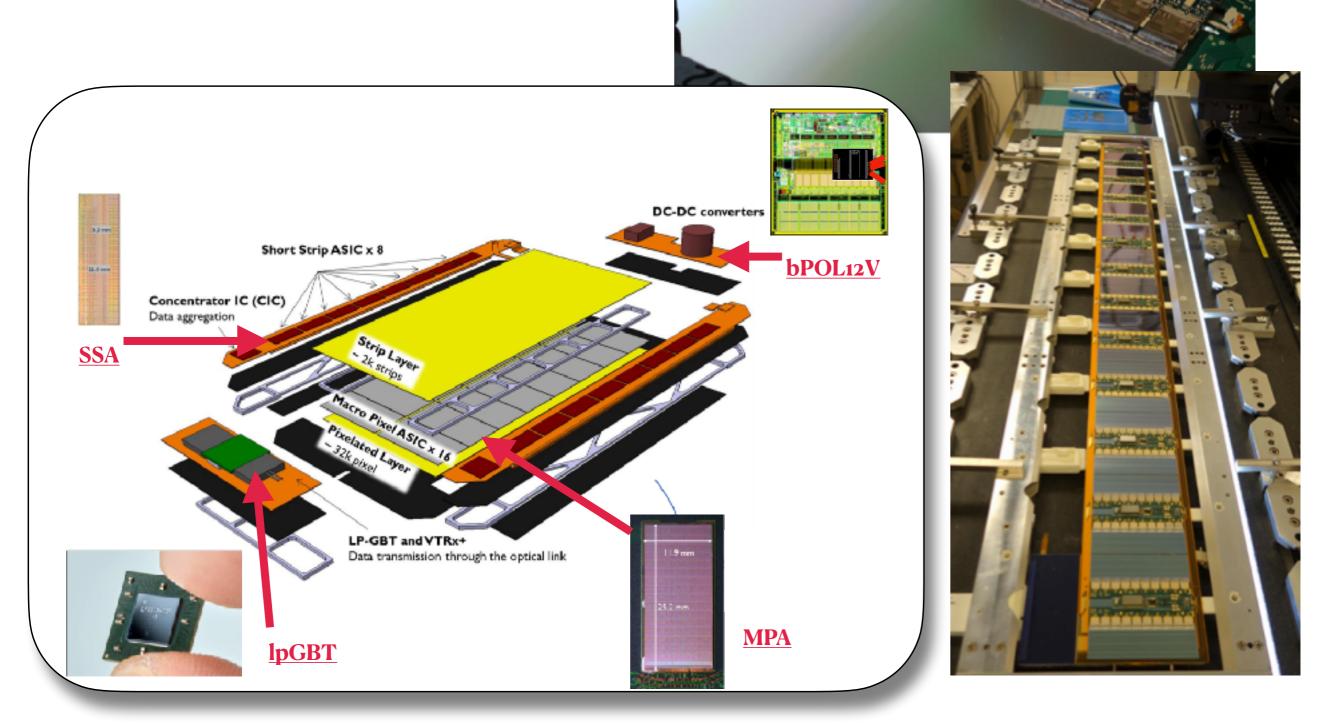

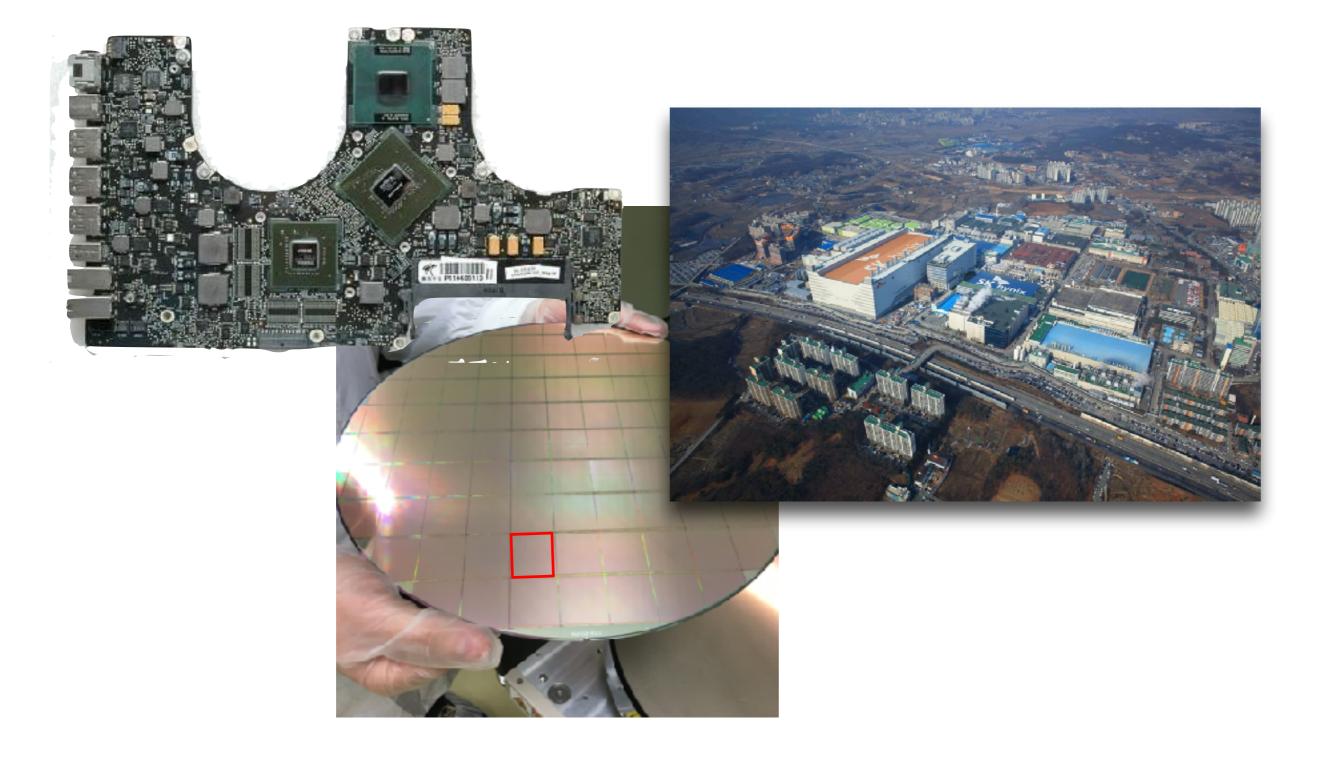

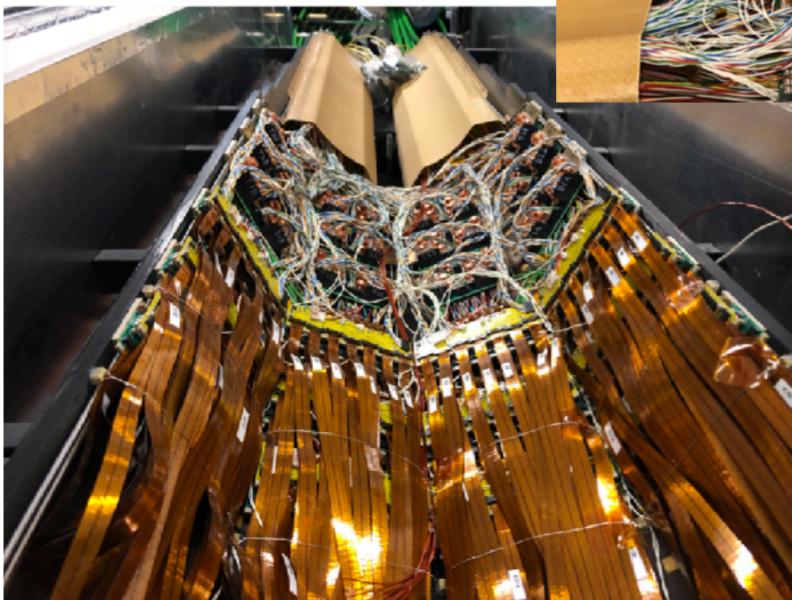

Integrated circuits (CHIPS) are used in High Energy Physics experiments...

Integrated circuits (CHIPS) are used in High Energy Physics experiments...

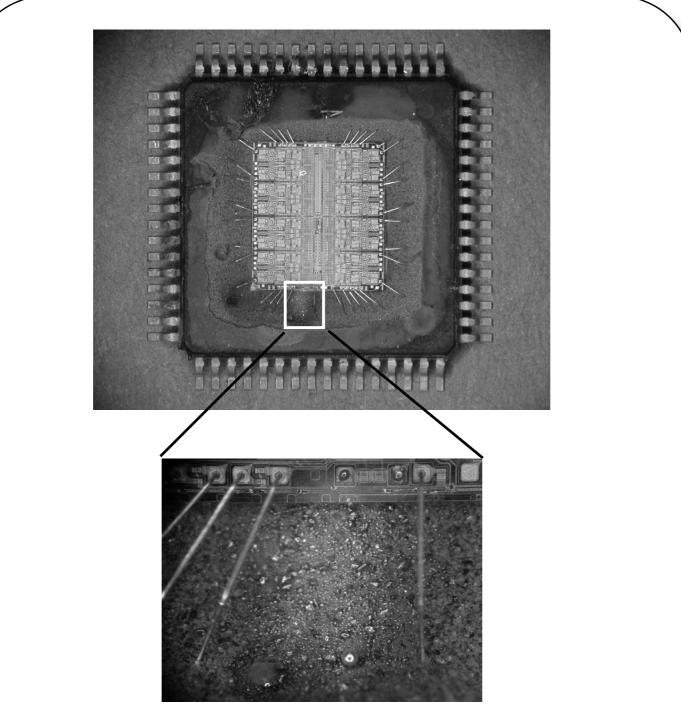

#### Inside the package

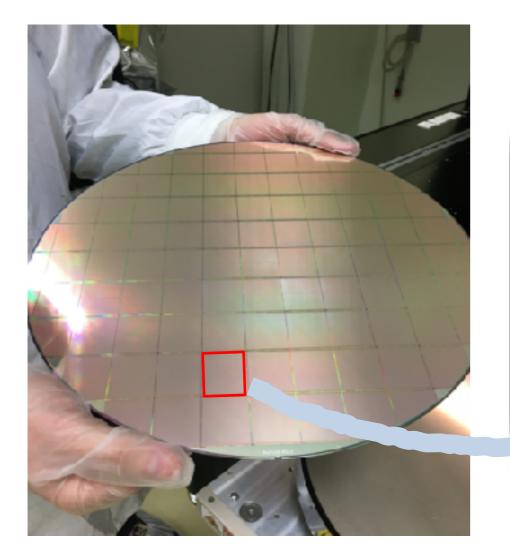

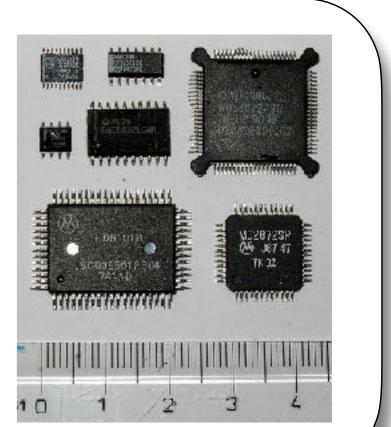

Integrated circuits (CHIPS) are manufactured on a silicon wafer, each containing a multitude of identical chips

After wafer dicing, individual chips are most often assembled in a plastic package

#### **Transistors to make a CHIP**

A CHIP is made up of transistors connected to form a circuit

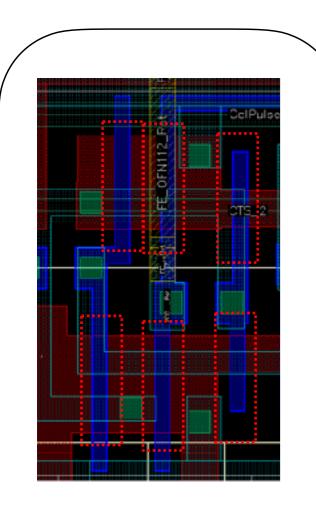

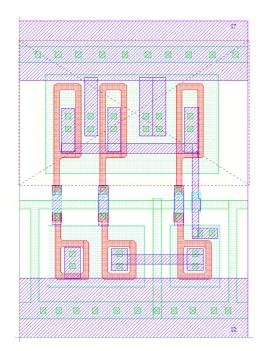

Drawing to manufacture 6 transistors (in the red squares)

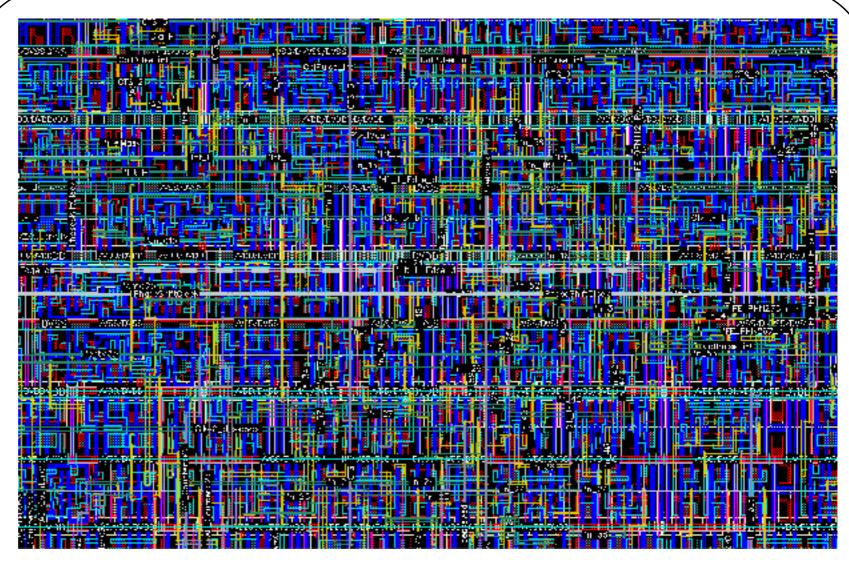

Thousands of transistors interconnected by metal lines

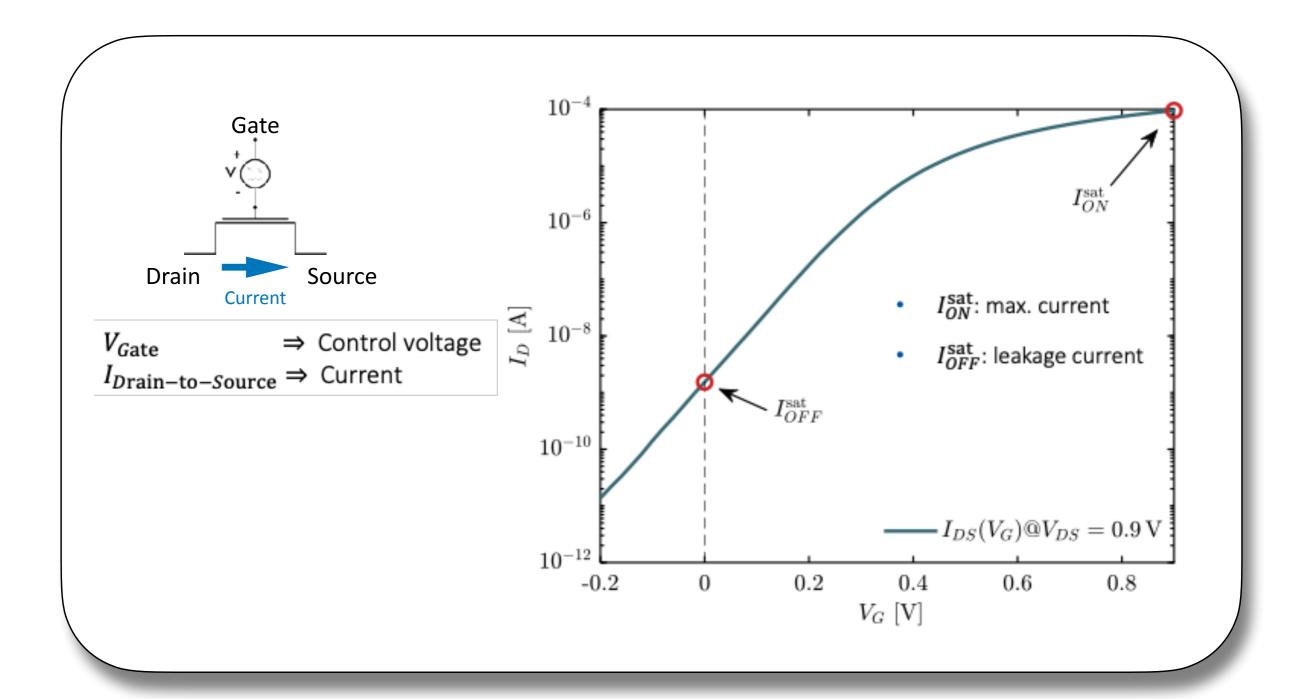

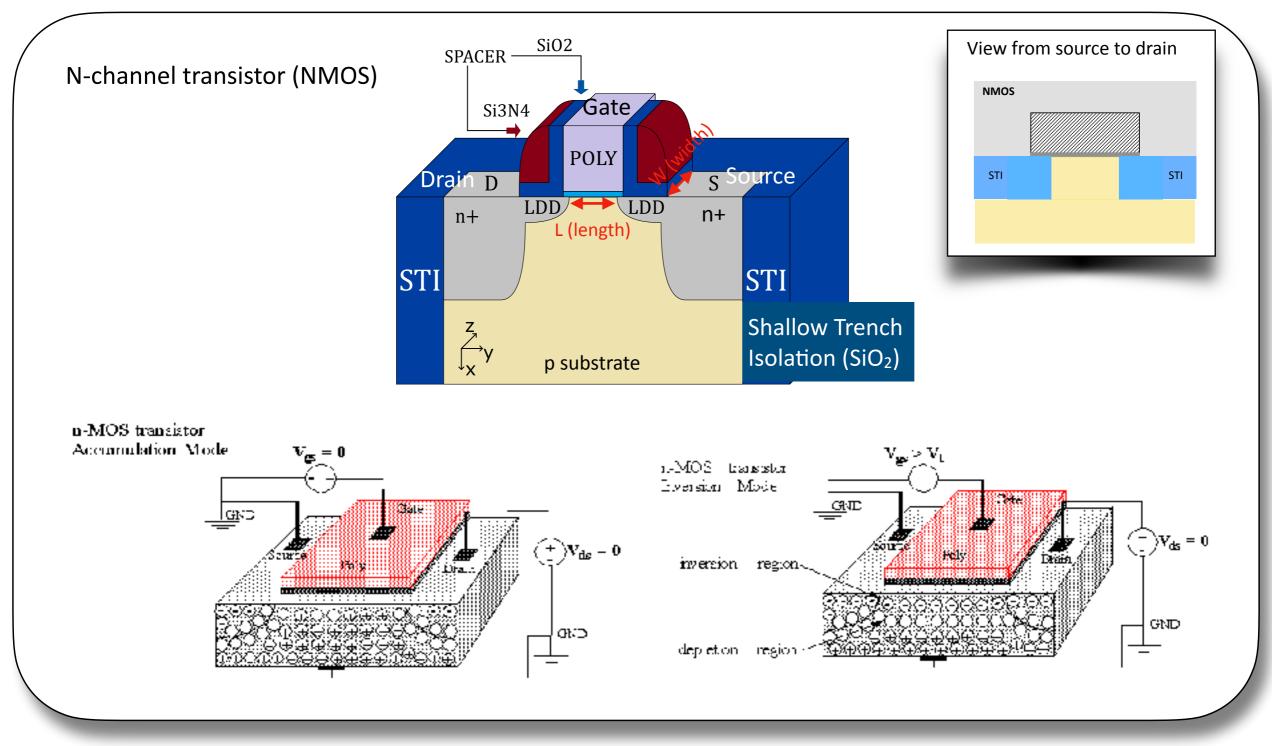

Transistors' drain-source current is controlled by the voltage applied to the gate and is proportional to the physical size (W/L, where W is the width and L the length)

## Transistors' drain-source current is controlled by the voltage applied to the gate and is proportional to the physical size (W/L, where W is the width and L the length)

P-channel transistors (PMOS) are the same but they have reverse polarity (n and p doped regions are inverted)

**CMOS** technologies use both NMOS and PMOS transistors

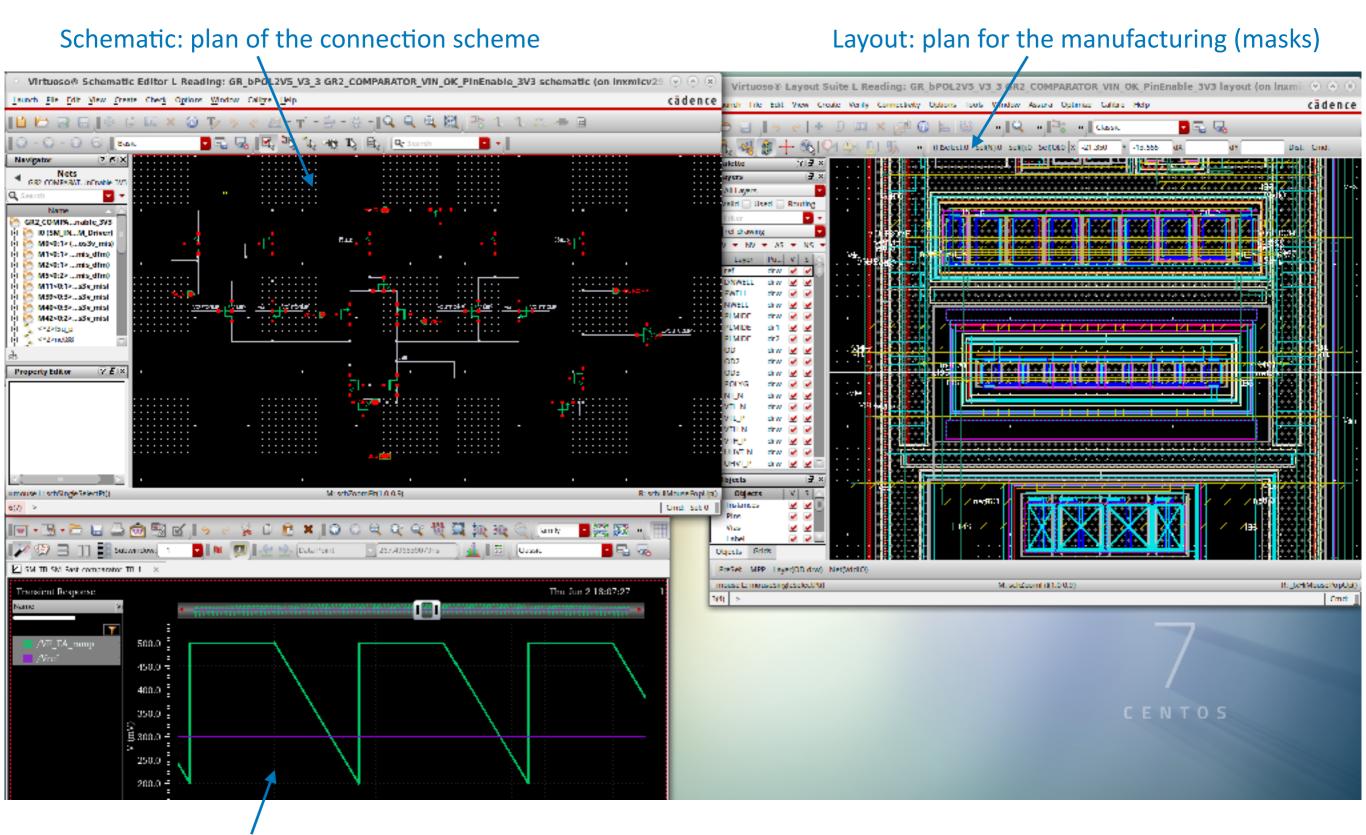

#### Connecting transistors to form a circuit: analog design

Simulation of the schematic: waveforms

#### Connecting transistors to form a circuit: high-level digital design

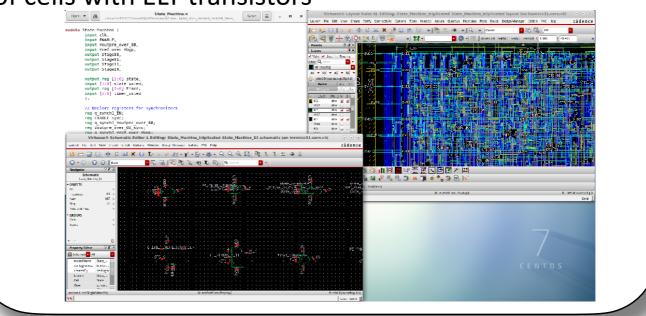

#### Layout: plan for the manufacturing (masks) Automatically generated Code: functional description of the circuit State Machine.v Virtuoso@ Layout Suite XL Editing: State\_Machine\_triplicated State\_Machine\_triplicated layout (on Inxmicv31.cern.ch) Sauce ≣ D X Oben 💌 迅 \_ Tohreas...igital\_block\_stacked\_tank/GR\_State ideviel20,V01 Launch Rie Edit. View Create Verify Connectivity Options Tools Window Assura Quaytus Roorplan Place Route Design Manager Cellbre PV3 leip. cädence rodule State Machine - nr 20 Claude input clk, » 🖬 Y 40.000 (Exelvable Set NED Set 00 K 1.390 input ENABLE, input Voutpre\_over\_90, Palett 733 input Vref over Vbgp, output Stage88, / Valić 🖌 Jaed 🖢 Rostina. output Stage81, her Q output Stage11, // drawing output Slage18, NS output reg [1:0] state. input [1:8] state voted, output reg [3:0] timer, imput [3:8] Liner\_voled Pu., V 5 );; drw 🗹 🗹 N2 // Declare registers for synchronizers reg q\_synch1\_EN; reg ENABLE sync; reg q synch1 Voutpre over 88; reg Voulpre\_over\_08\_sync; N5. rea a synchl Vret over Vbas: Virtuoso® Schematic Editor L Editing: State Machine triplicated State Machine 13 schematic (on inxmicv31.cern.ch) • cādence aunch hie beit. View Create Creck Options Window Design Manager Calibre 1995 Help 1 些 🖷 🖻 35 0 💿 🛛 Вън O • O ≤., - 10 I 44 -16 16 巨) • Navigator $\nabla F$ 91 1 2 Schematic 🔨 😼 🗟 📐 State, Machine, 15 OBJECTS 10:102955 ЛÌ Moseshtil(conclusplay) R: IoHiMouseAppl.p() Sances Ornd | 107 Netz Pins Nets and Pins GRO UPS Cells Ispes. 7 E × **Property Editor** 🧟 Schemaŭ 🔽 All State\_... modelName. CENTOS verlogi orma. Inféri Verlingi created by Library State . mouse LoschSindeSele Ond: Sel: 9

Blocks used by the automatic generator (pre-existing in a library with physical description and electrical parameters)

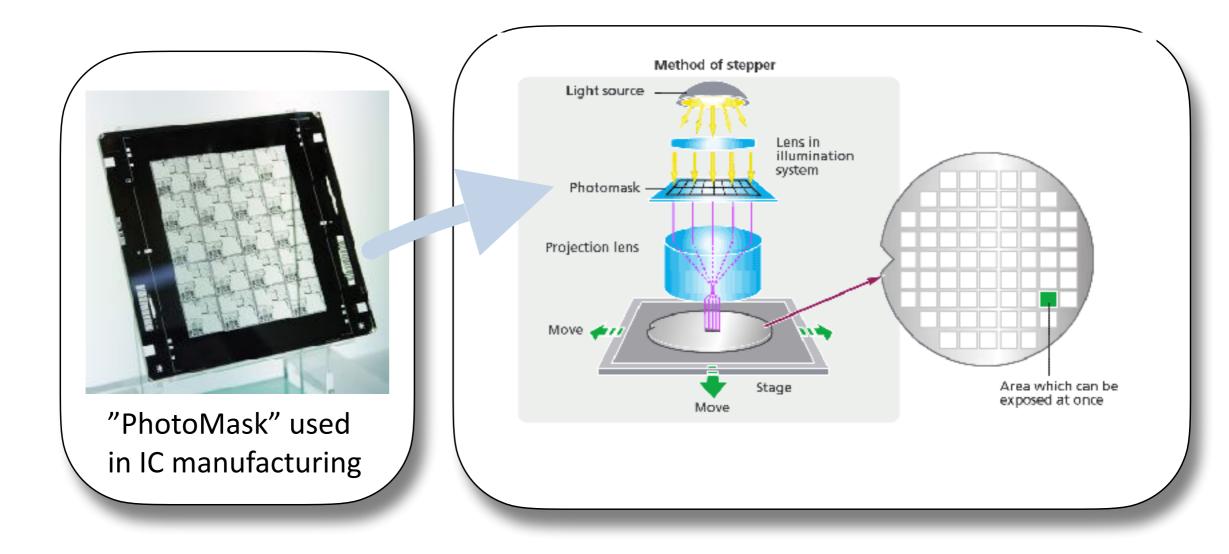

#### Printing 10<sup>12</sup> tiny transistors in a CHIP

All features (transistors, connection lines, ...) are manufactured by "printing" features on the silicon wafer, then exposing the printed zones to specific processing steps.

Images are first produced on "PhotoMasks", then printed – on a much smaller size – on the wafer using very complex lithographic steps

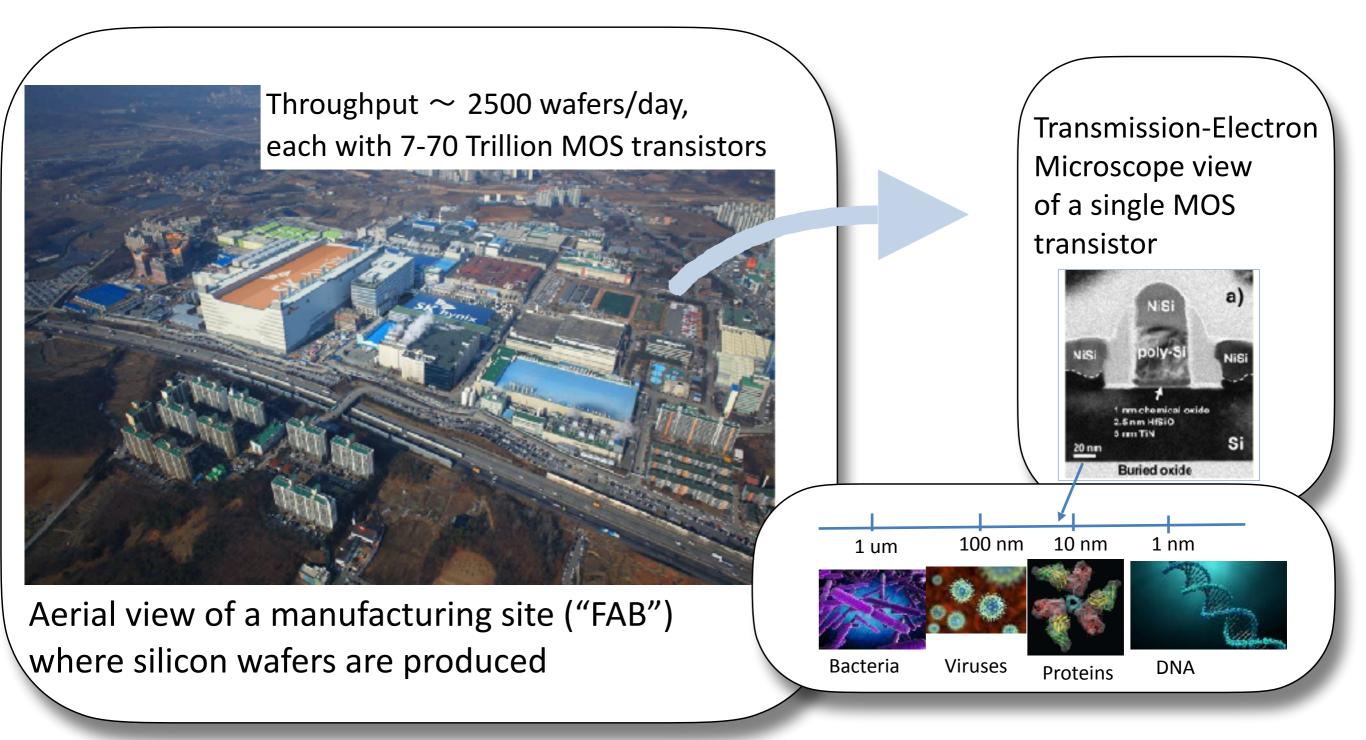

### Silicon Wafer Manufacturing

A giant to make a tiny dot

### Silicon Wafer Manufacturing

Look inside a giant "FAB"

Wafers travel through processing equipment in sealed vessels

Very few human operators are needed

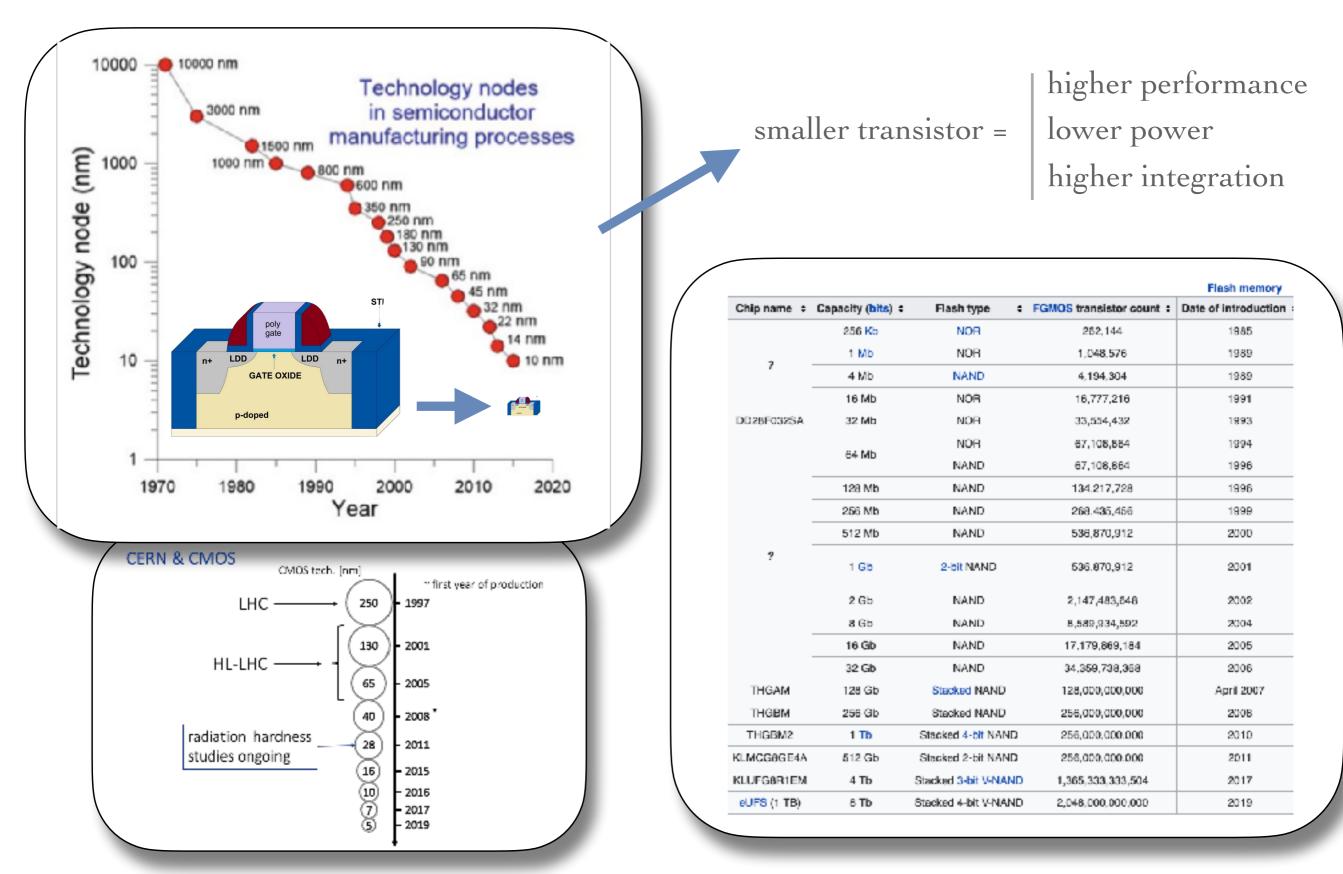

## The semiconductor industry has strived to scale the size of the CMOS transistors to smaller dimensions

Each generation is characterised by the minimum printable shape (called technology "Node")

### Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

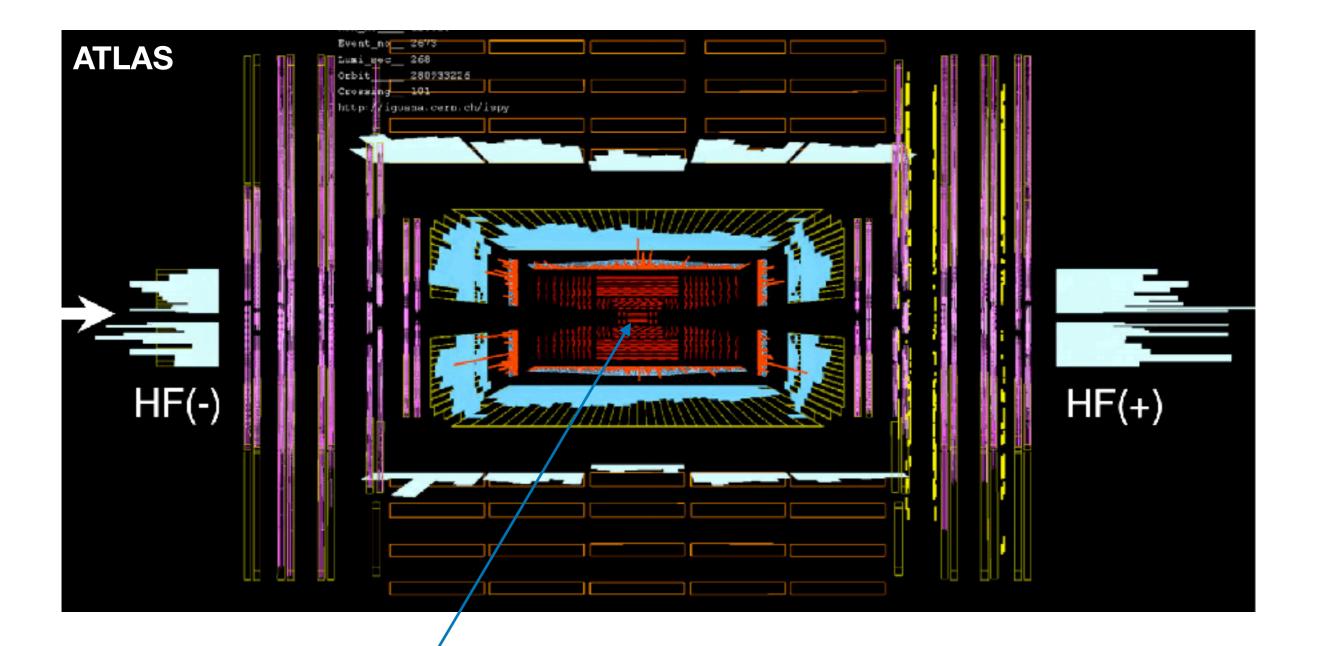

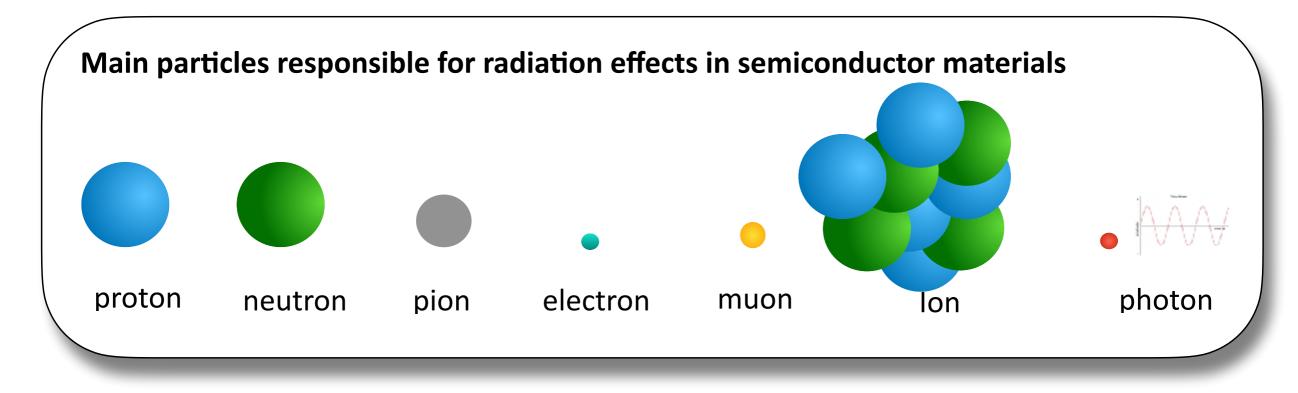

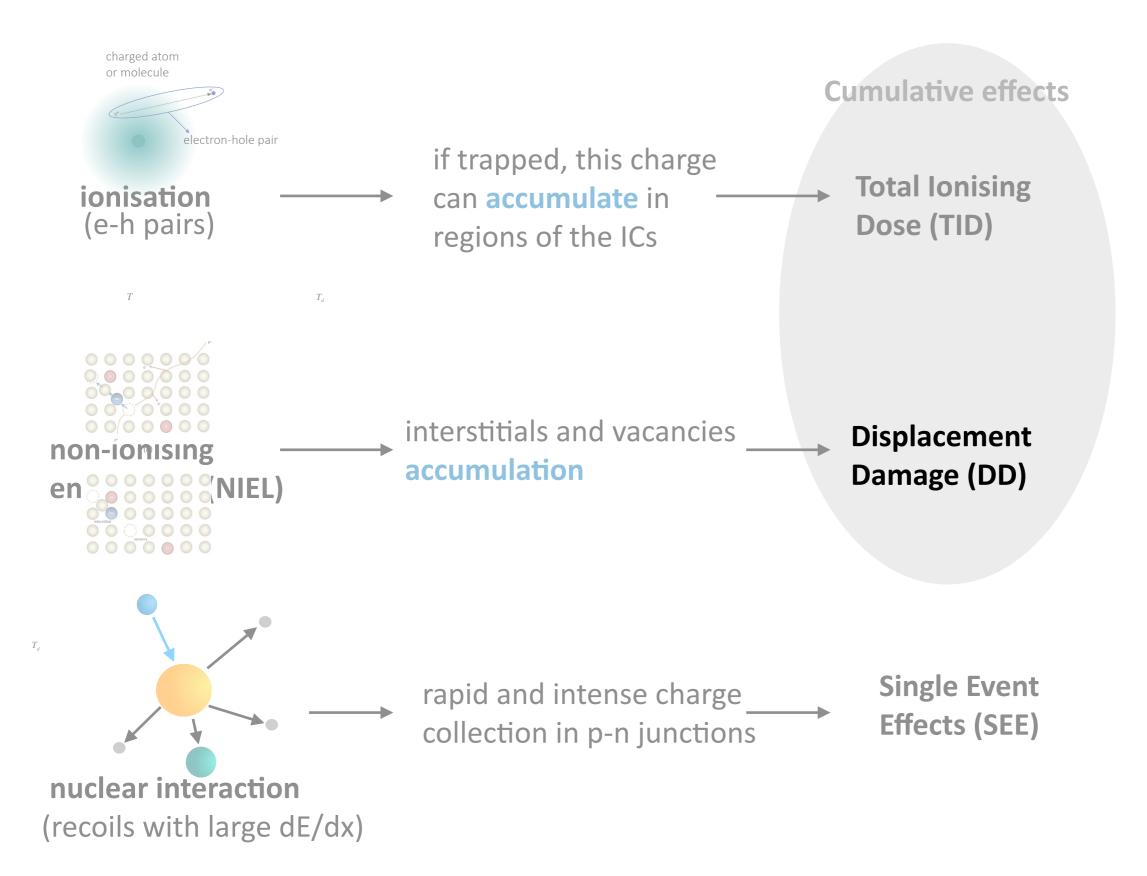

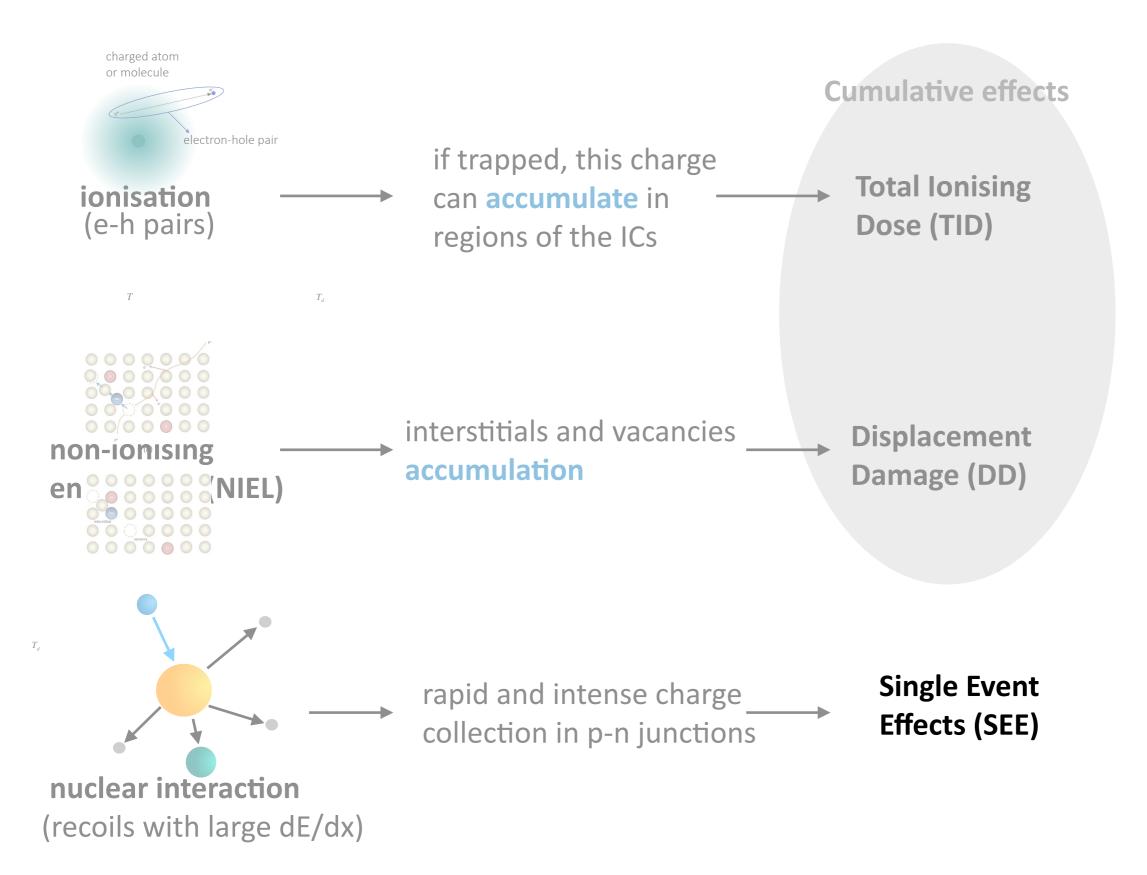

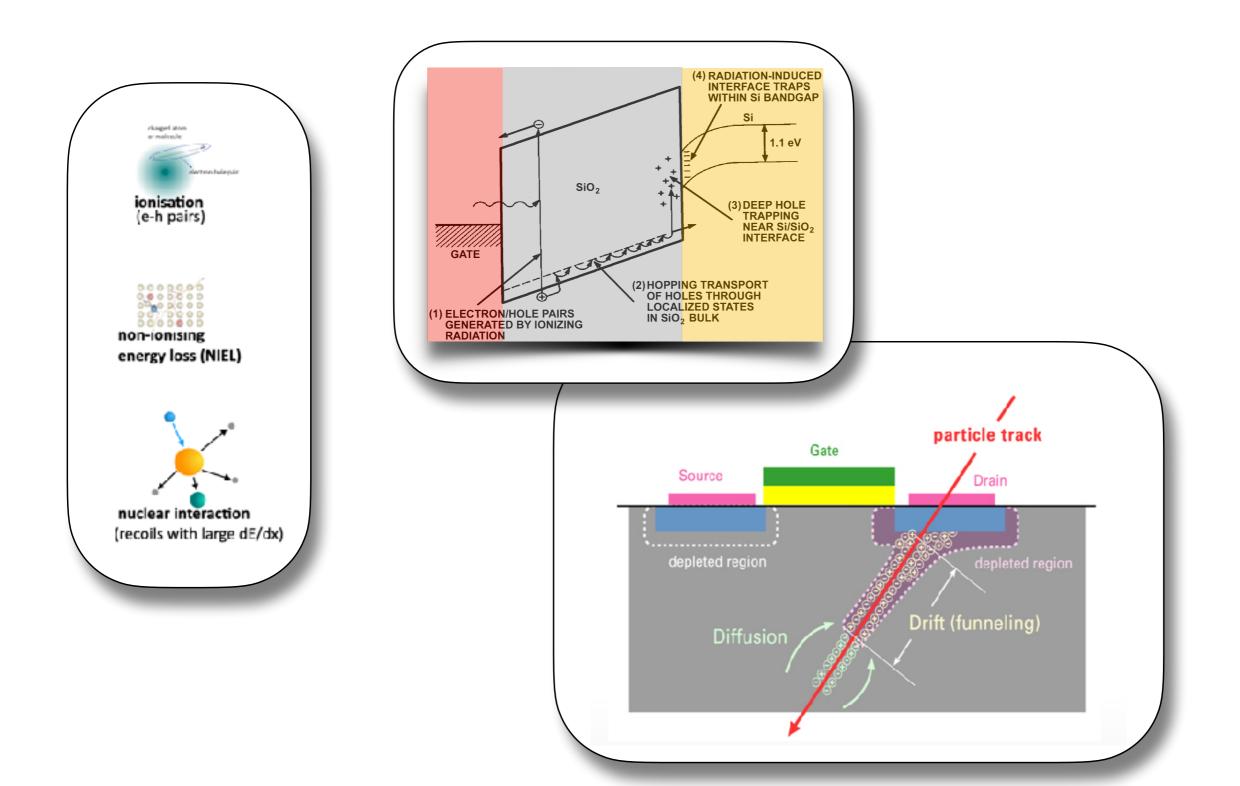

The electronics in the LHC experiments is immersed in a radiation field generated by the p-p collisions at their center.

Collisions at the center: the radiation field is more intense in the inner detector layers and decreases with the distance.

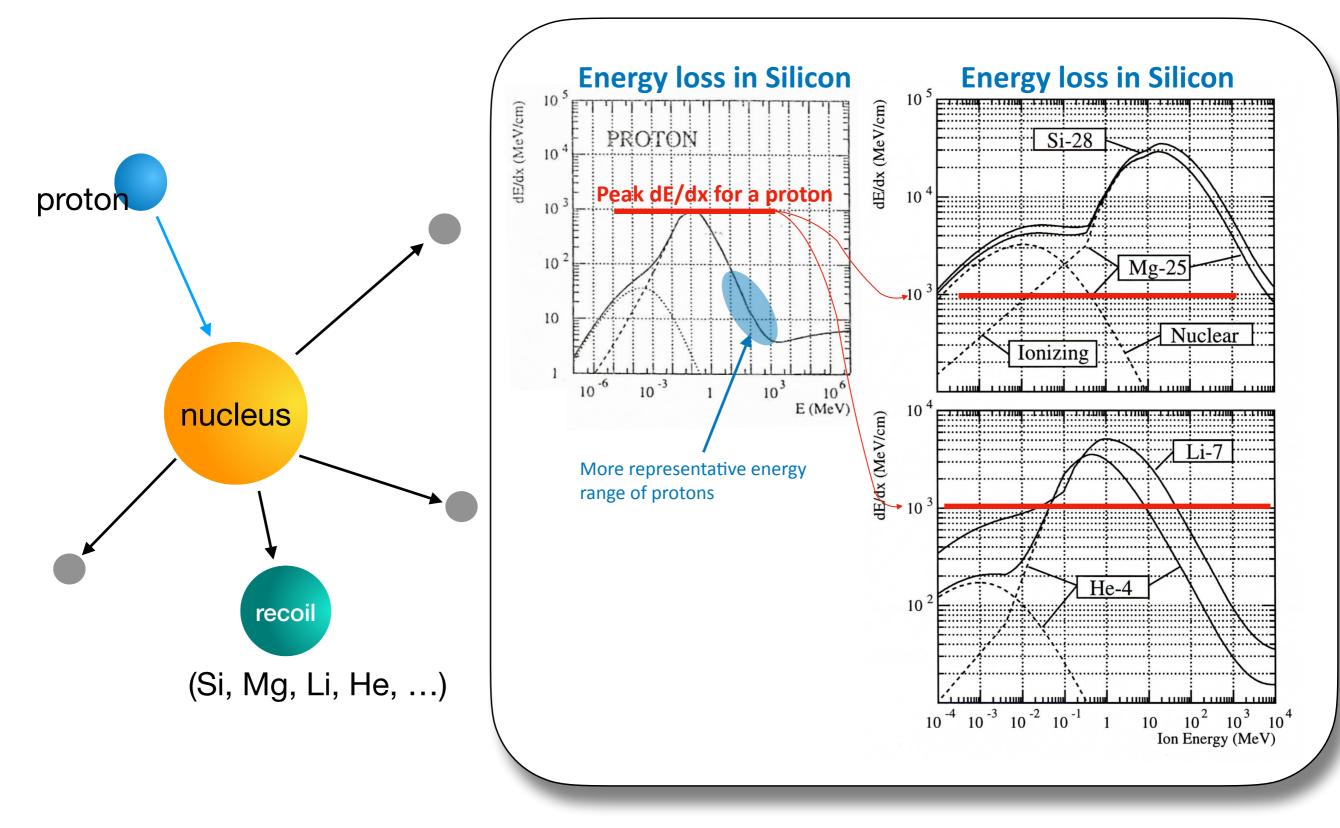

Energetic protons interact with atoms in the material they traverse.

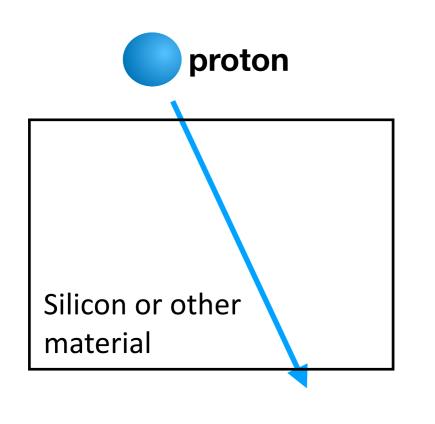

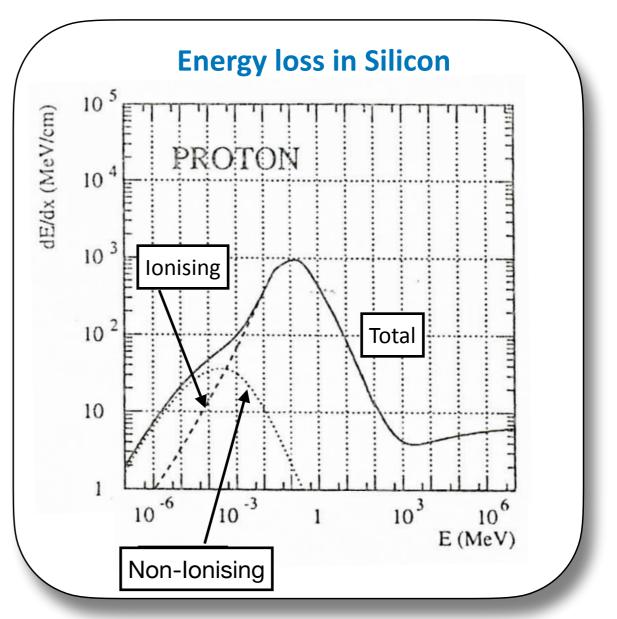

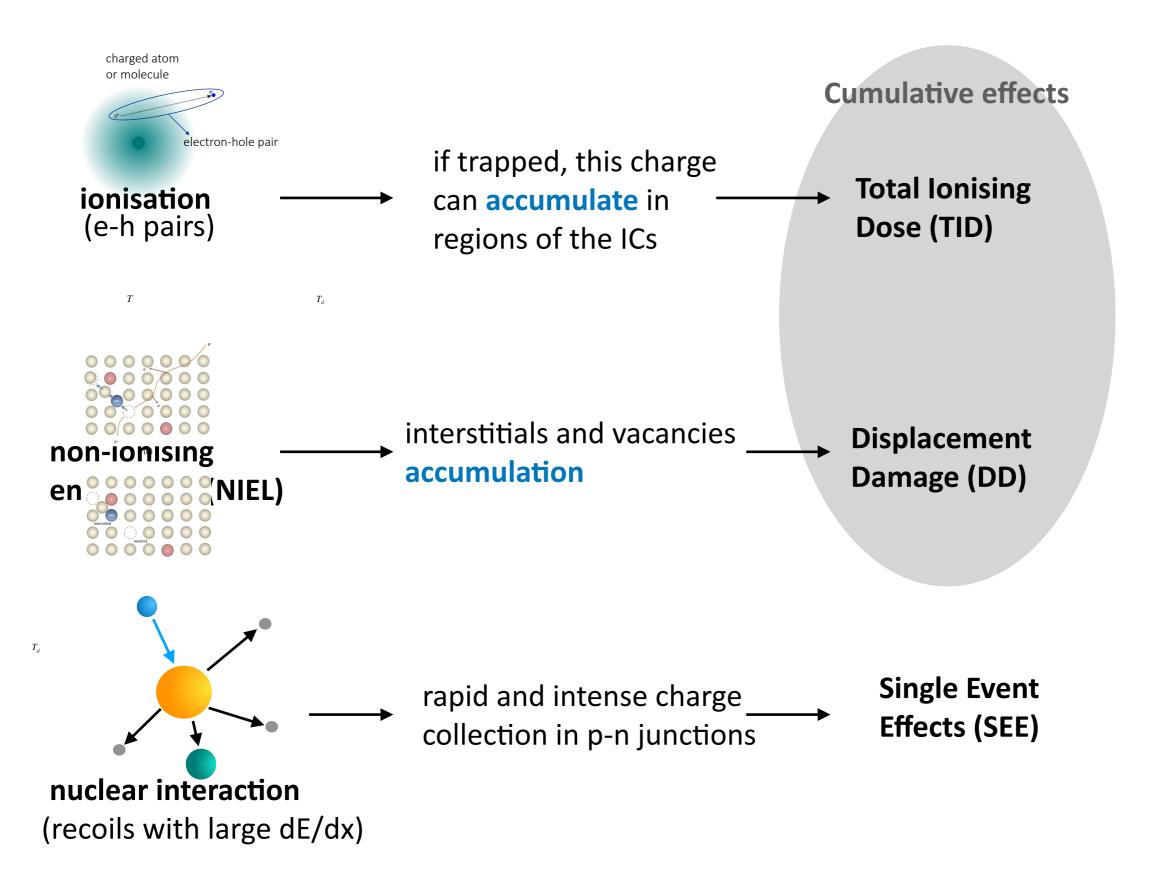

They can loose energy per unit path length via <u>ionising</u> or <u>non-ionising processes</u>.

(a)

interstitial

after C.Virmontois, "Displacement Damage in optoelectronic devices

for space applications", Short Course at the 2017 RADECs, Geneva

vacancy

(b)

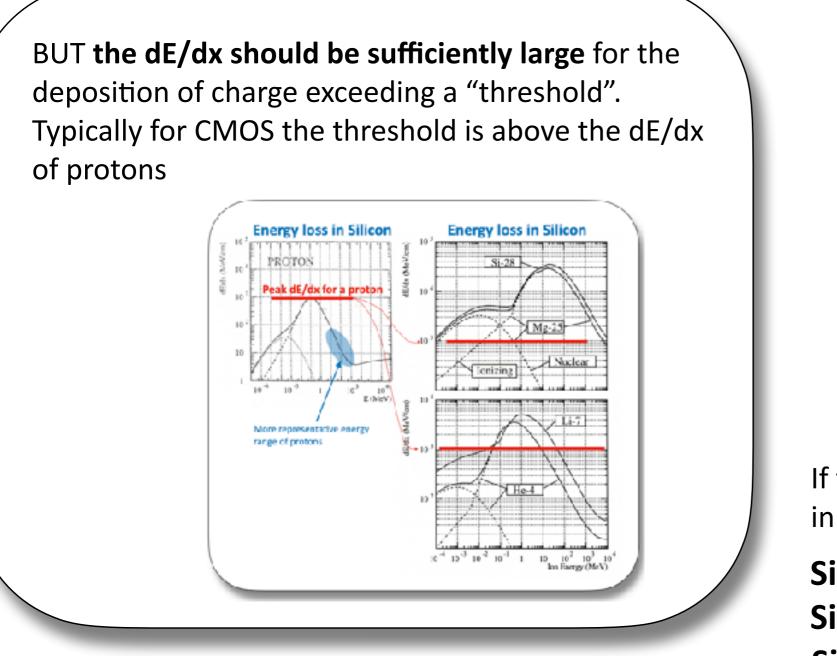

#### Non-Ionising Energy Loss (NIEL):

atoms are displaced from their regular position in the lattice, giving origin to interstitials and vacancies. The disturbance in the crystal lattice periodicity has associated discrete energy levels in the forbidden energy band-gap. These influence generationrecombination processes in the material. Neutrons, protons and pions can also interact with the nuclei of the material (if their energy is sufficient to overcome the repulsive electrostatic barrier of the nuclei). Typically this will produce a shower of secondary particles and one nuclear recoil (Si, Mg, Li, He, ...) with much higher dE/dx and small range.

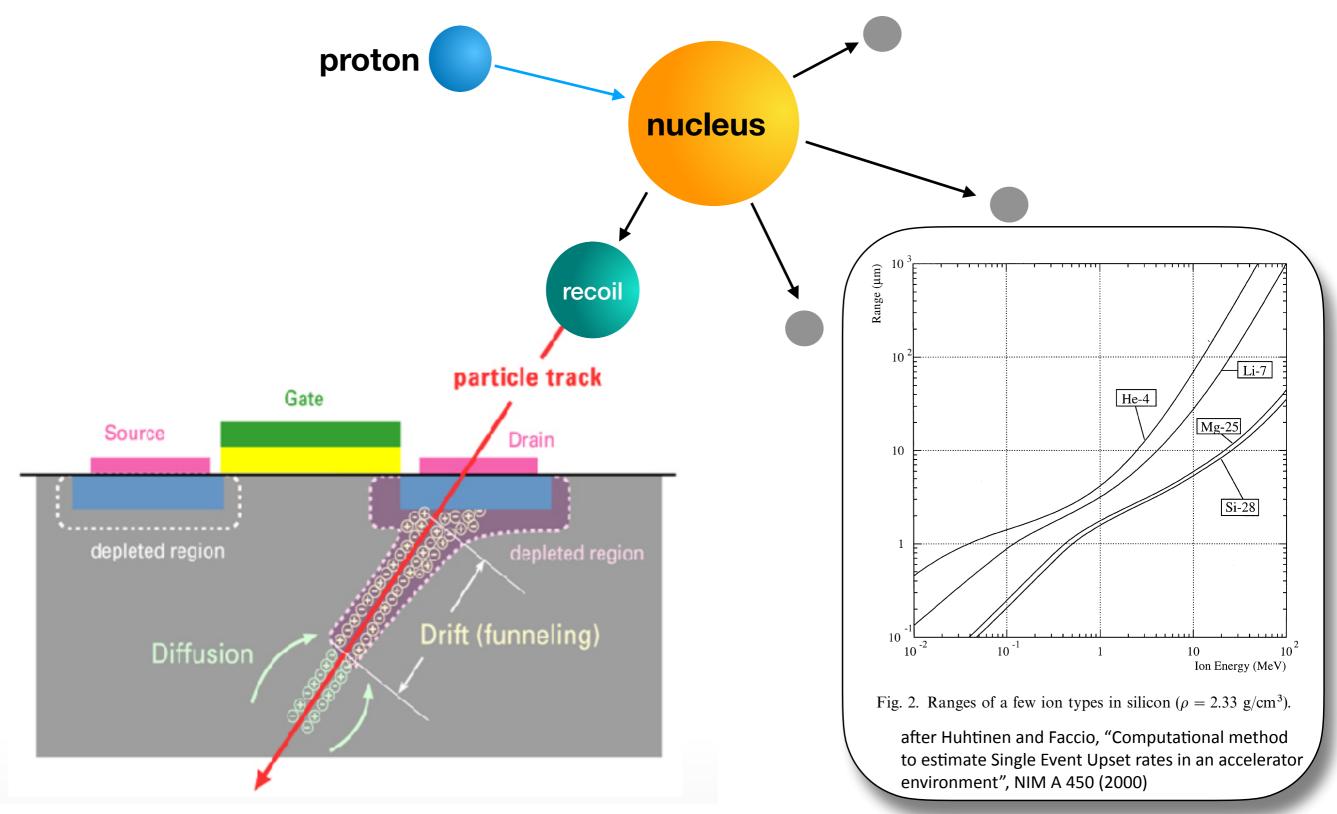

When a recoil with high dE/dx crosses a biased p-n junction, a large amount of charge can be collected rapidly at the electrodes.

These recoils have short range, so they must come from an interaction in proximity of the junction (order of 1-10um for the recoils with high dE/dx)

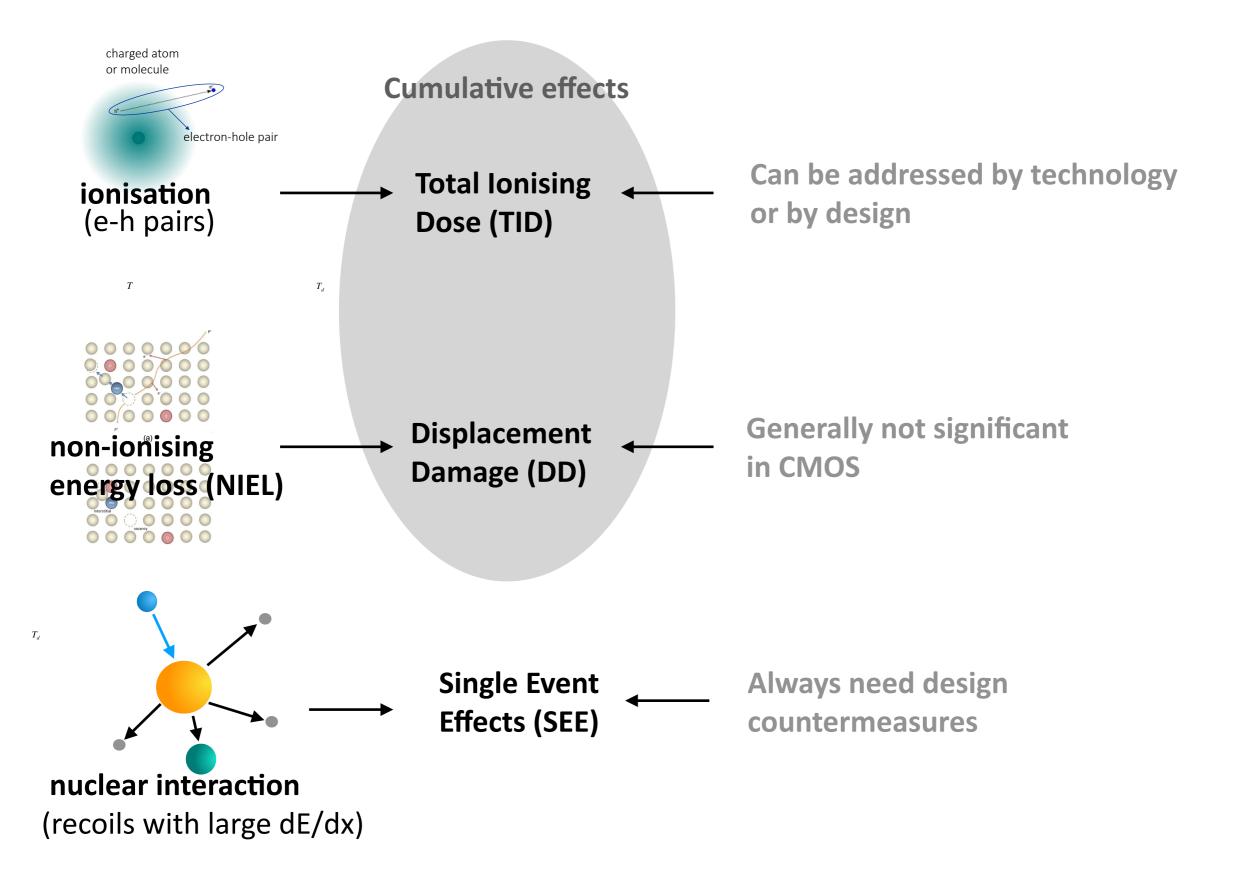

#### Summary

### Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

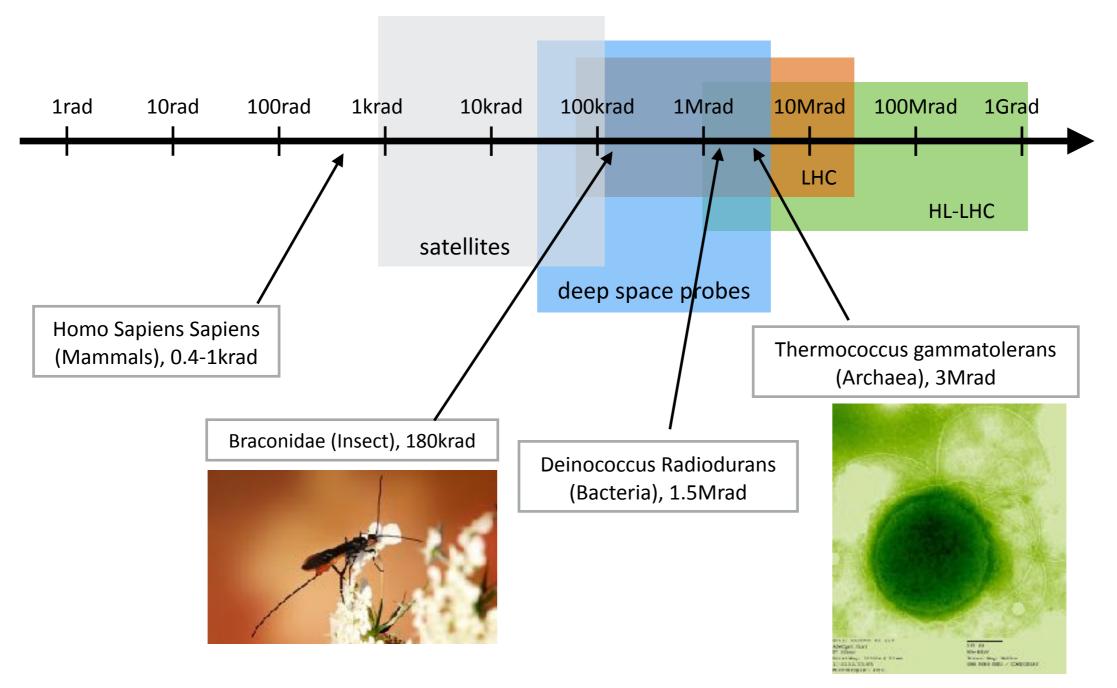

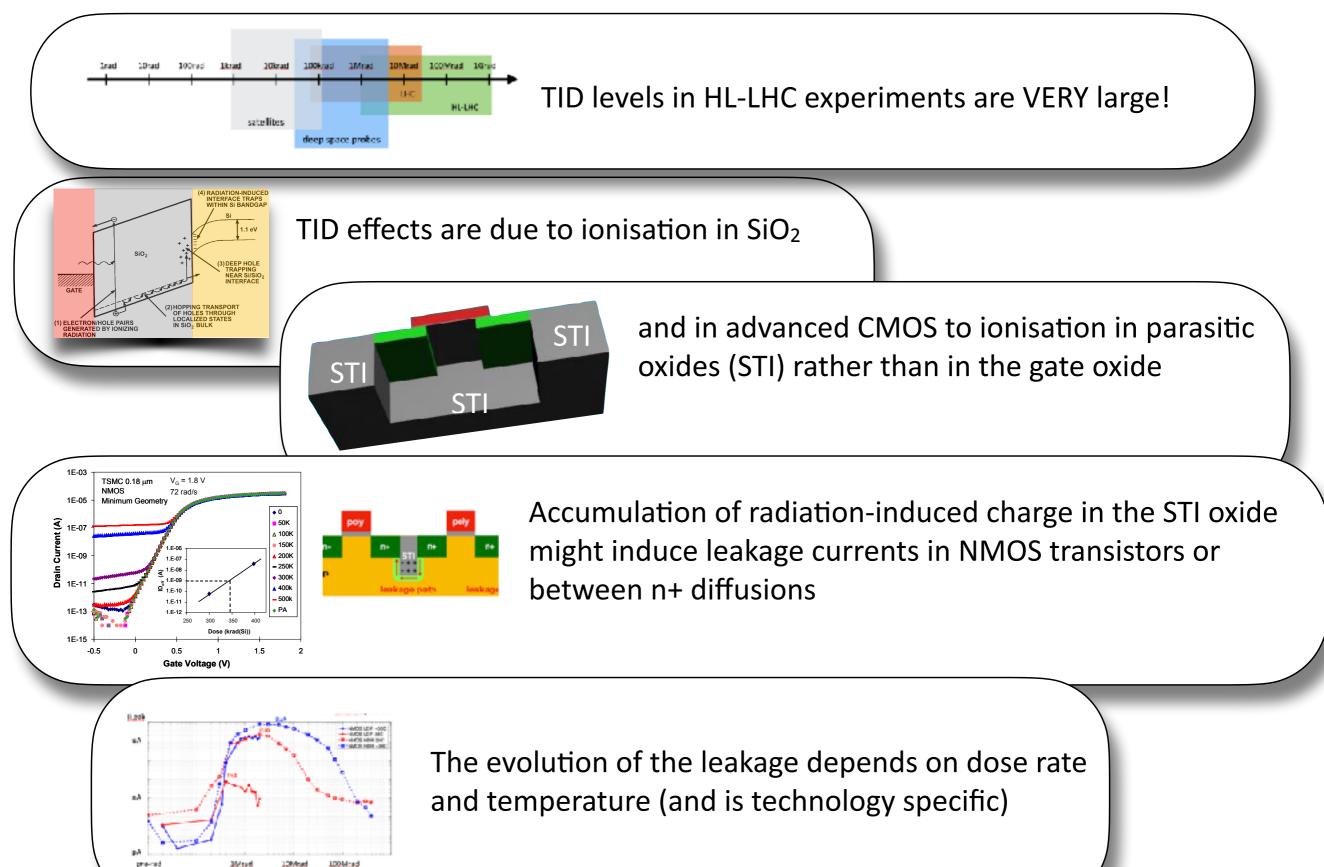

## Total Ionising Dose (TID) effects are traceable to the ionising energy loss in the material, generally SiO<sub>2</sub>

The unit for deposited dose is the Rad

(in the international system it is the Gy, where 1 Gy = 100 rad)

can be killed in 20minutes in our X-ray facility

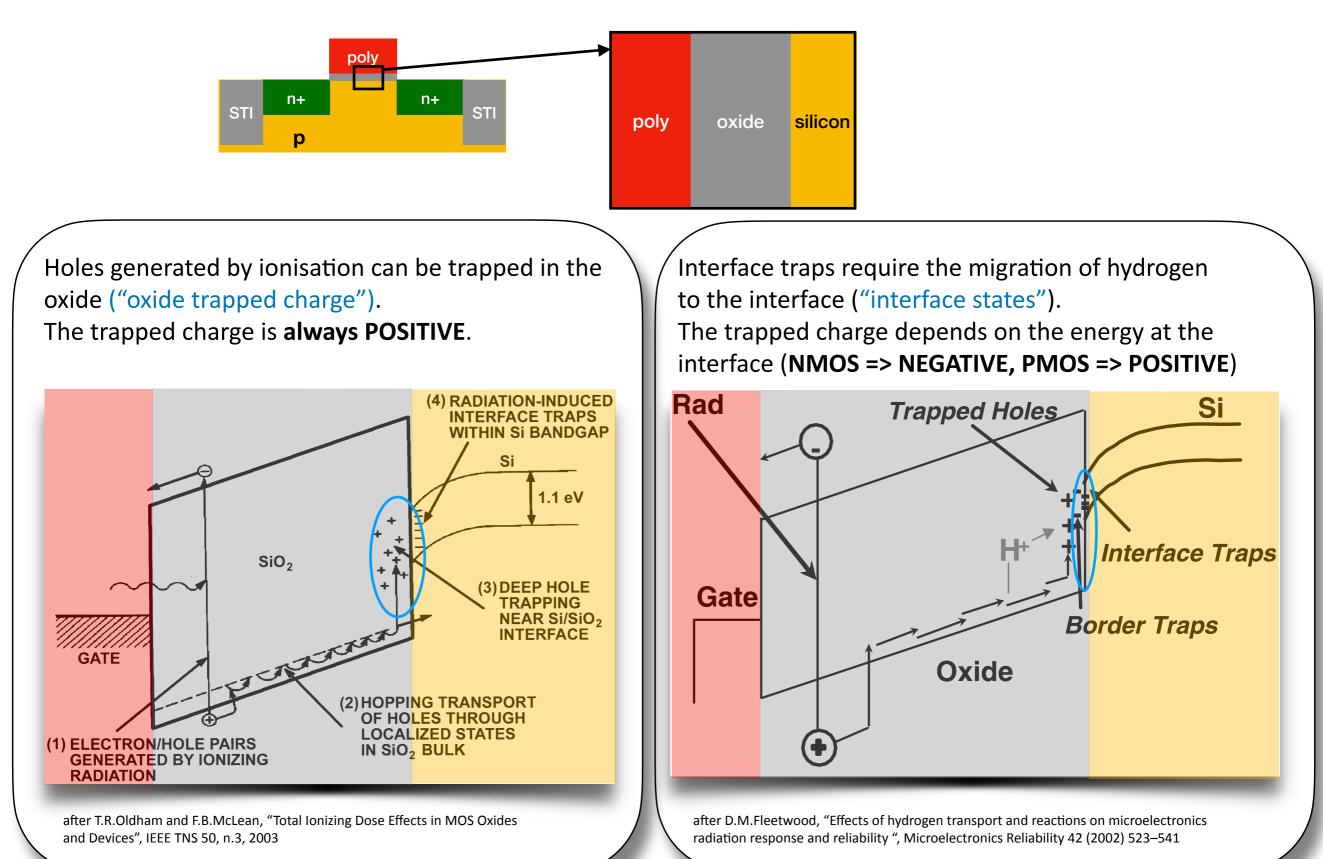

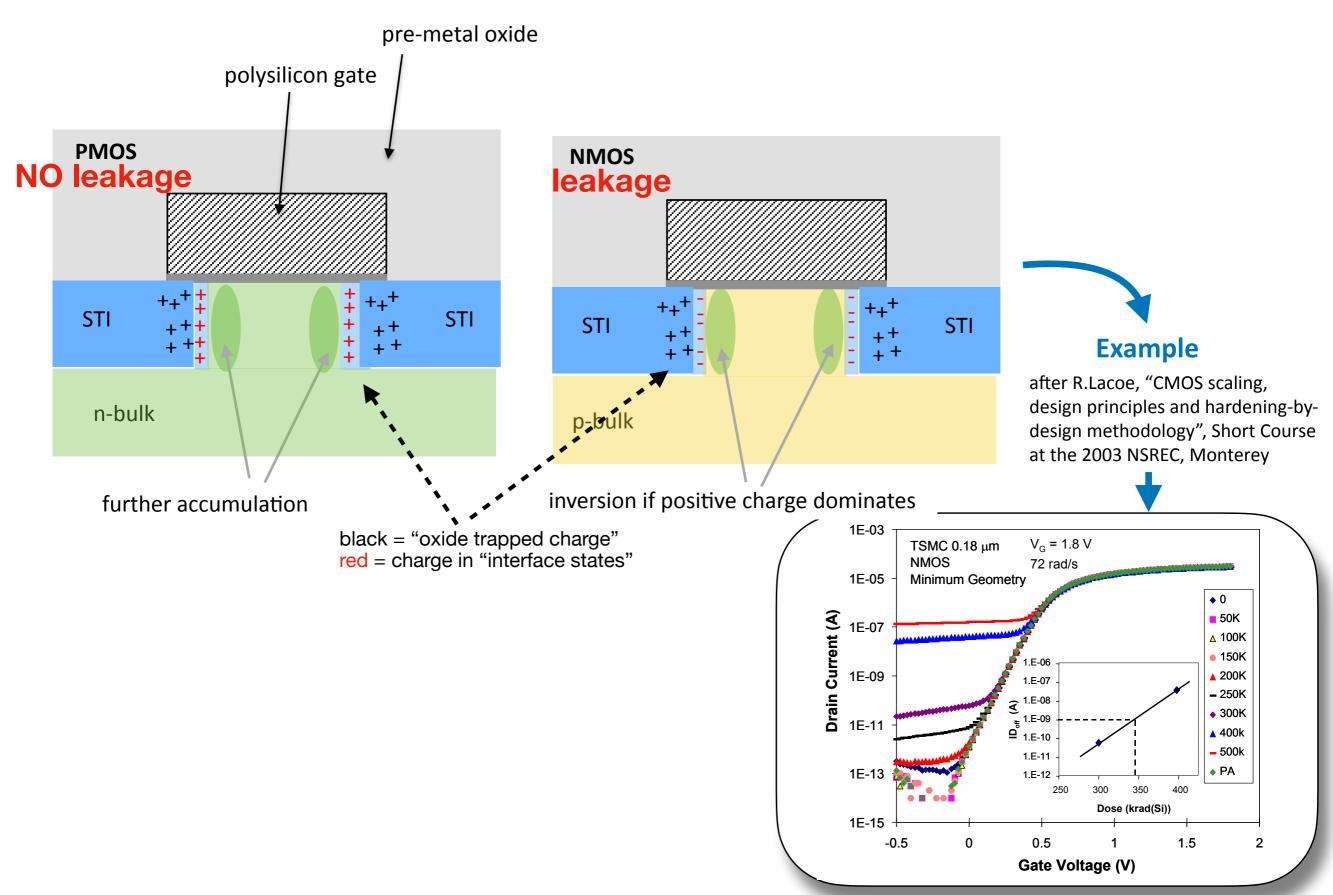

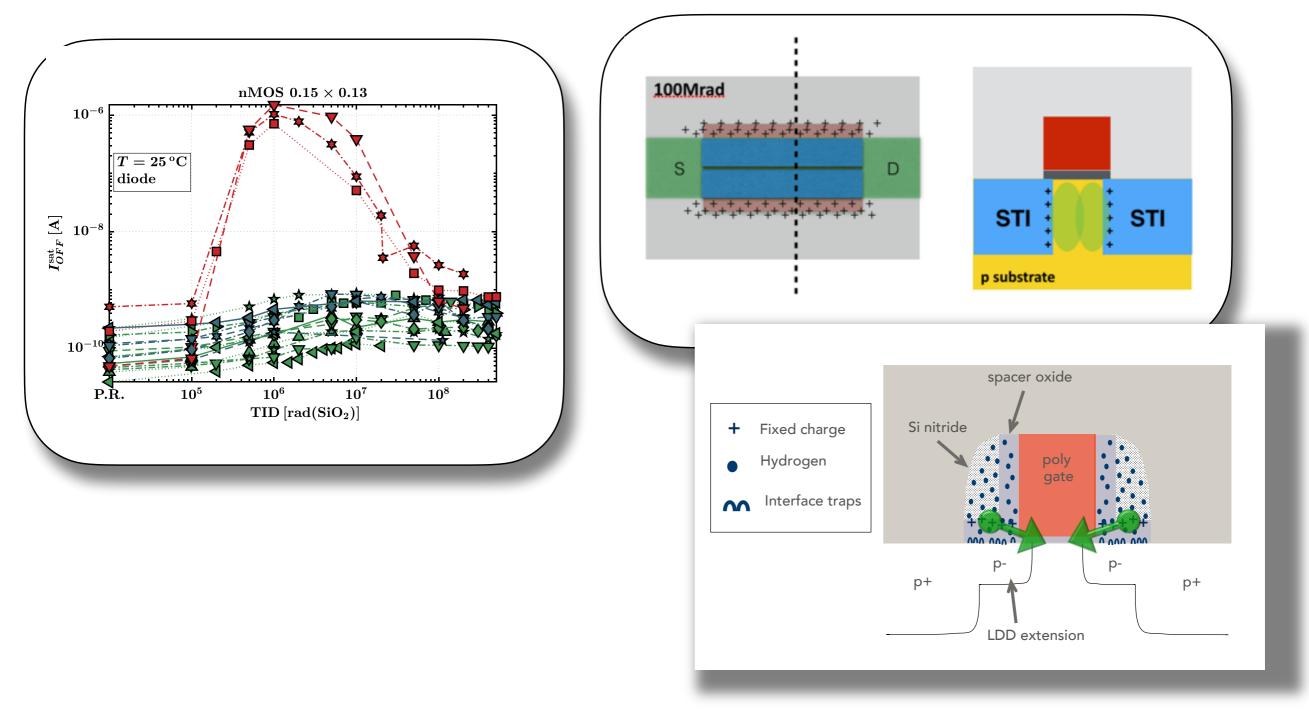

# TID-induced transistor degradation is due to charge trapped in the SiO2 or at its interface with the channel

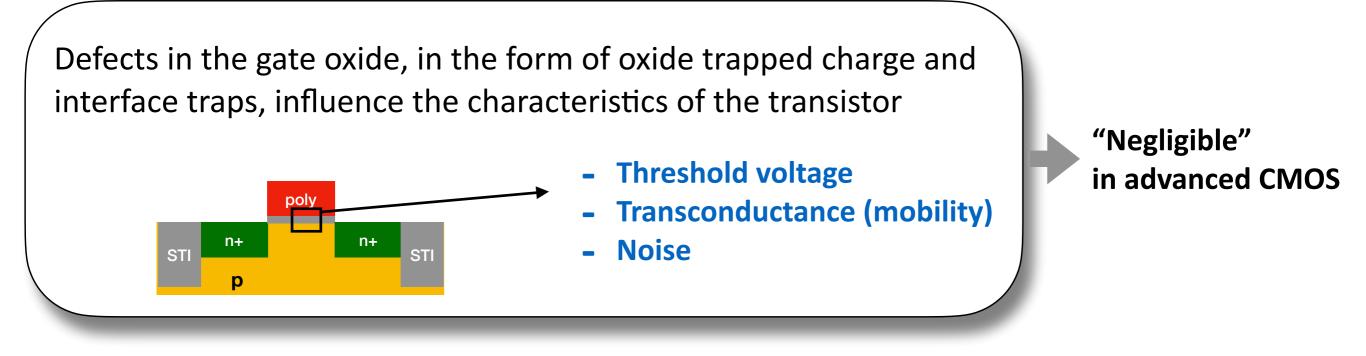

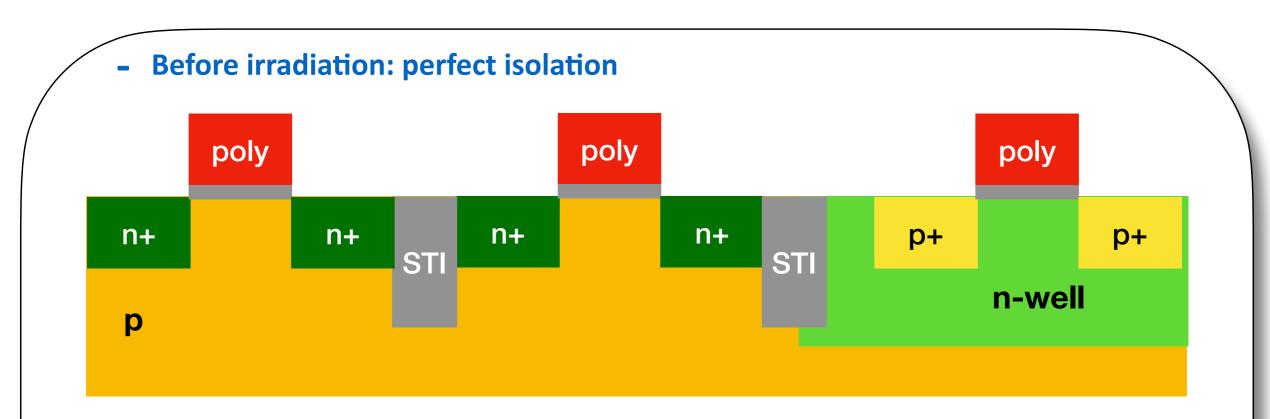

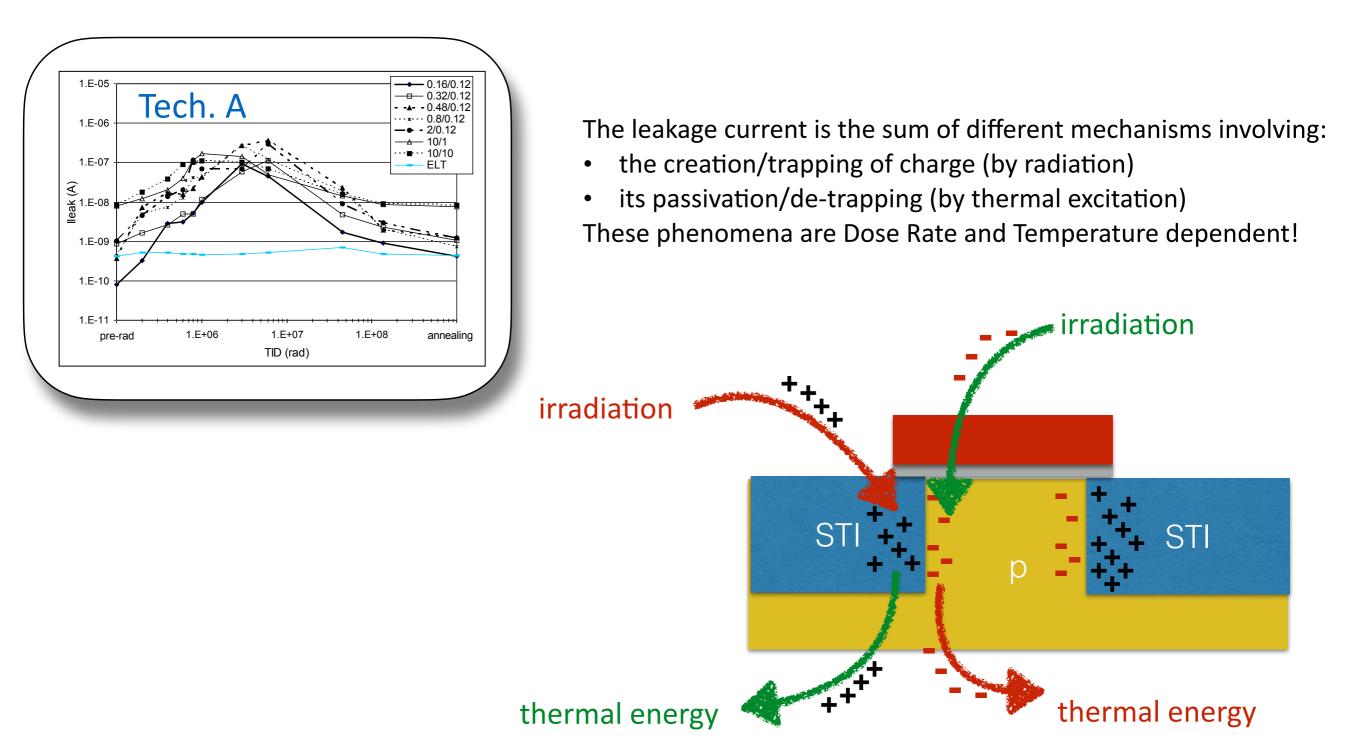

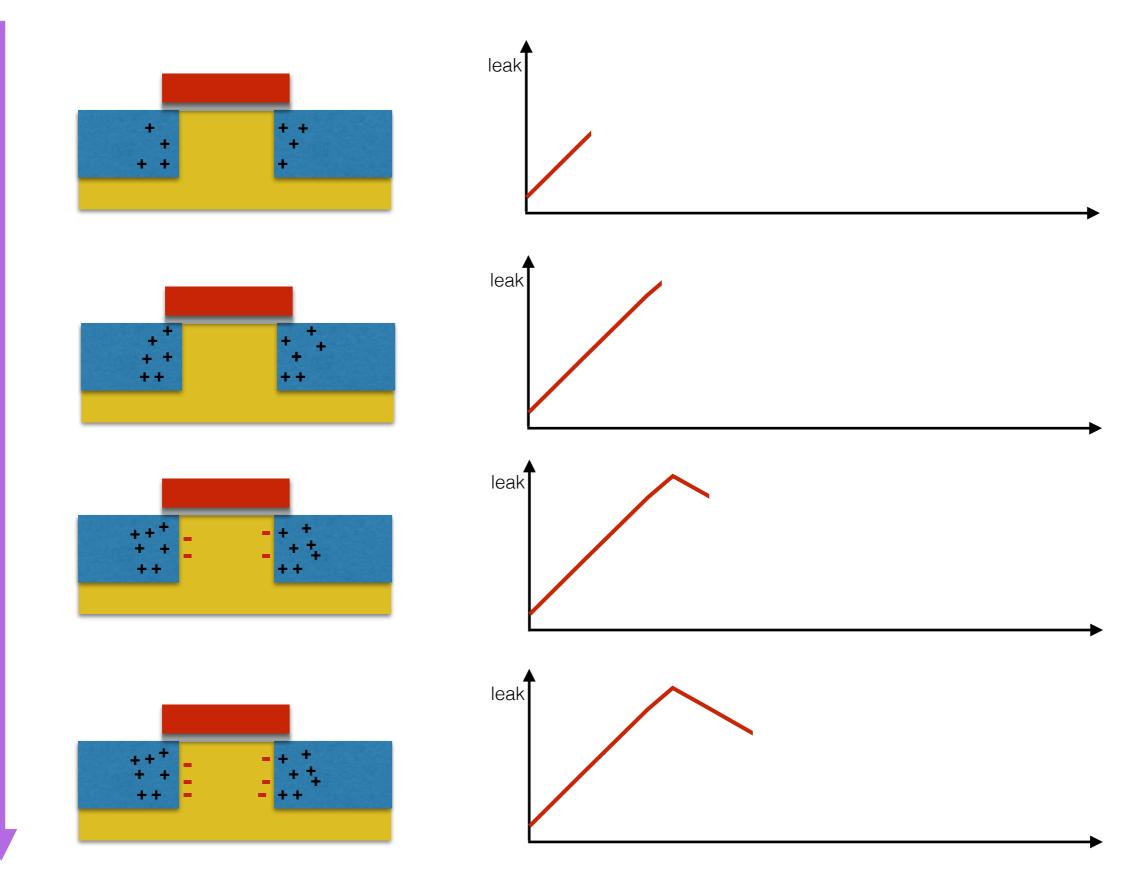

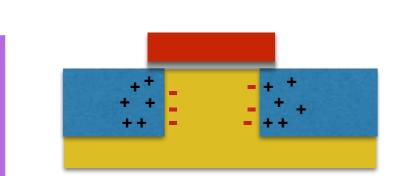

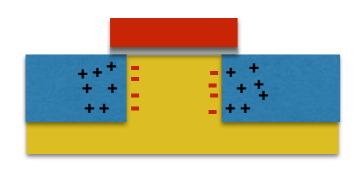

Defects in the field oxide (separation between transistors) might give origin to leakage currents

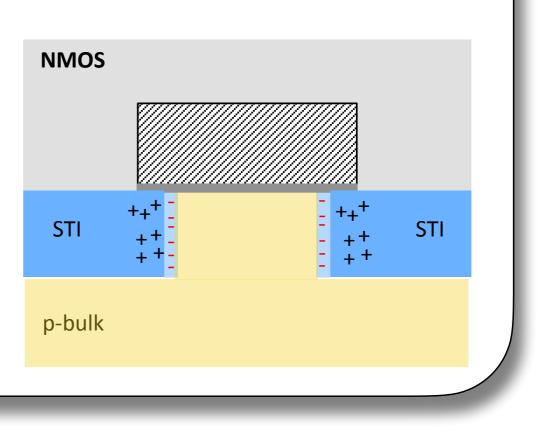

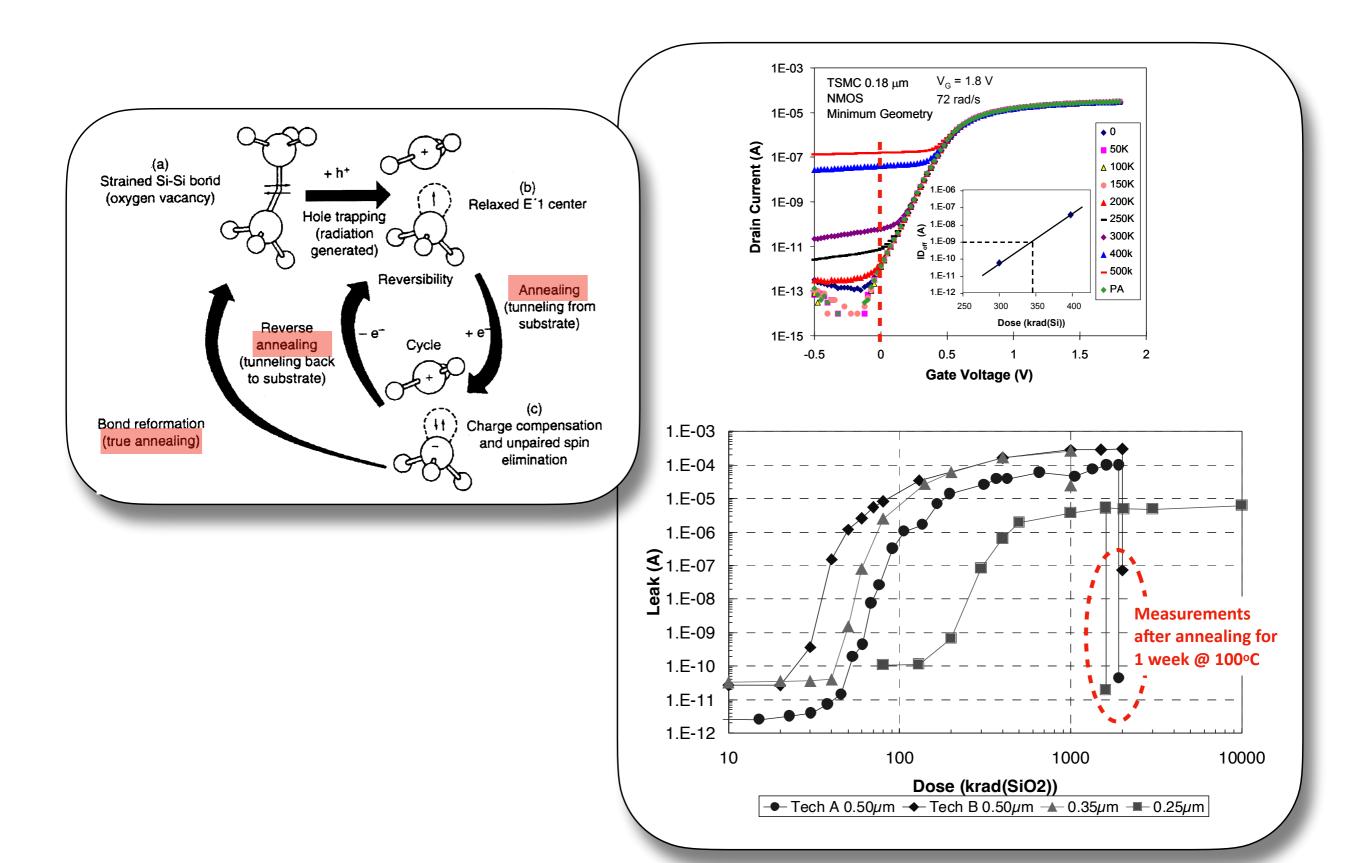

# Defects in the field oxide might give origin to leakage currents in NMOS transistors only

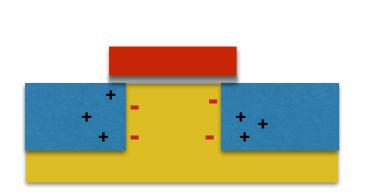

# Positive charge trapped in the STI oxide can also open leakage current paths between n+ diffusions at different potential.

Again, this might be mitigated (or suppressed) by negative charge in interface traps.

- After TID accumulation: leakage paths between adjacent transistors and wells

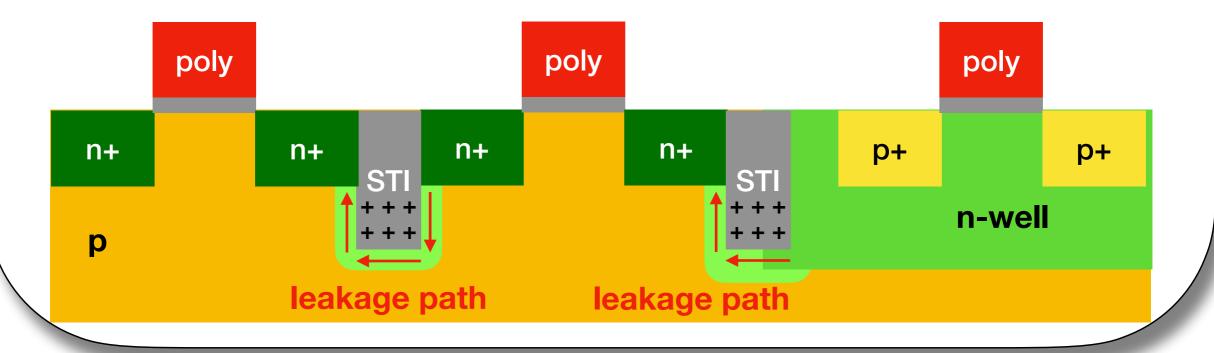

#### **Radiation-induced defects can "anneal"**

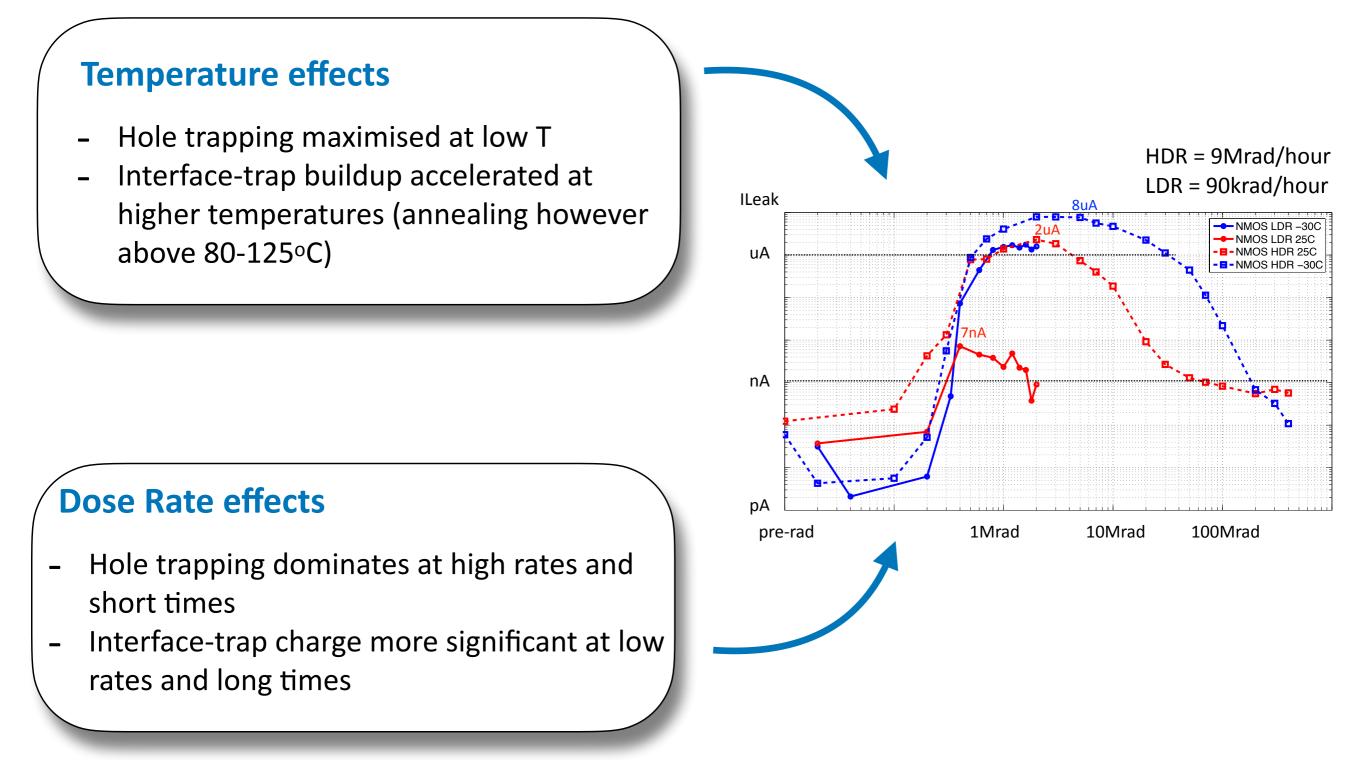

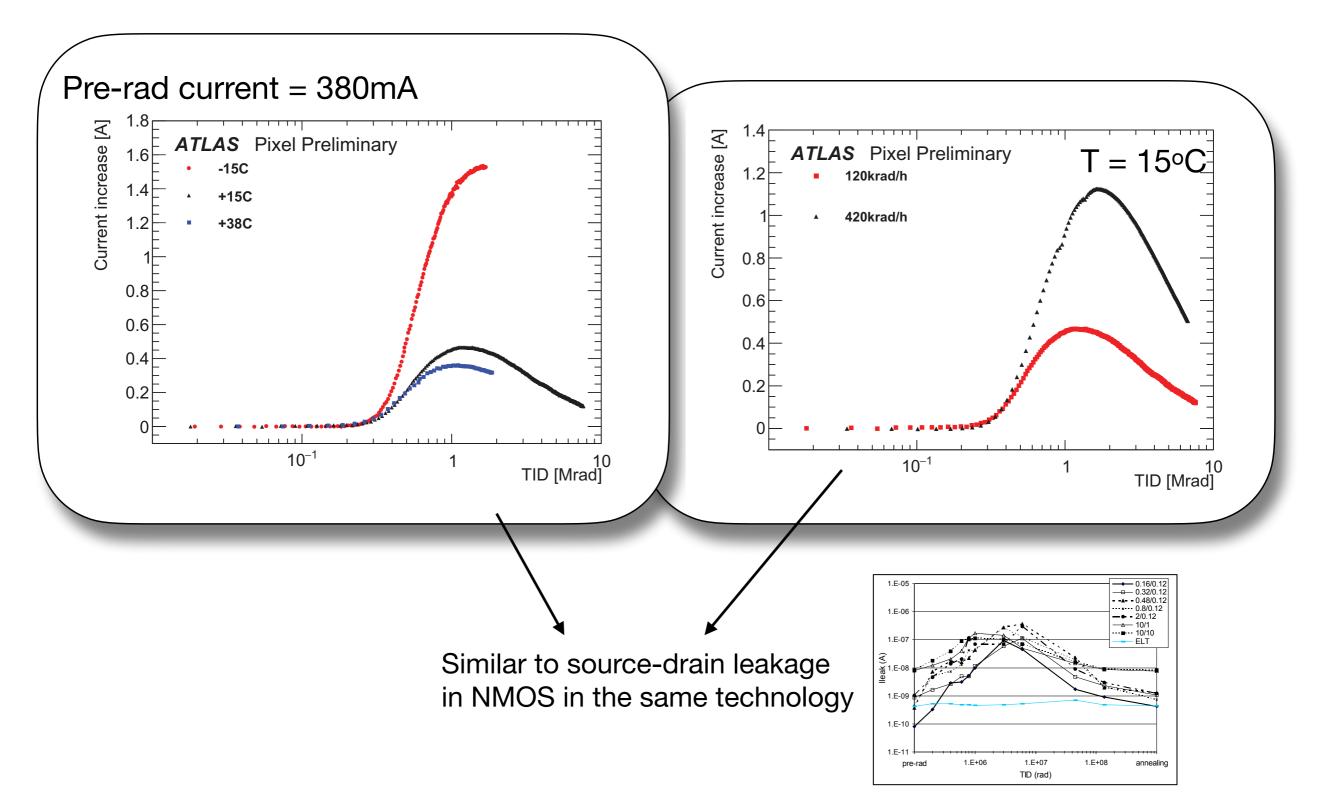

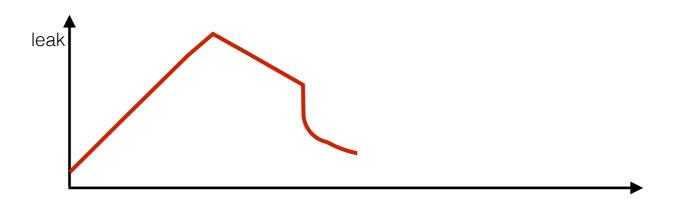

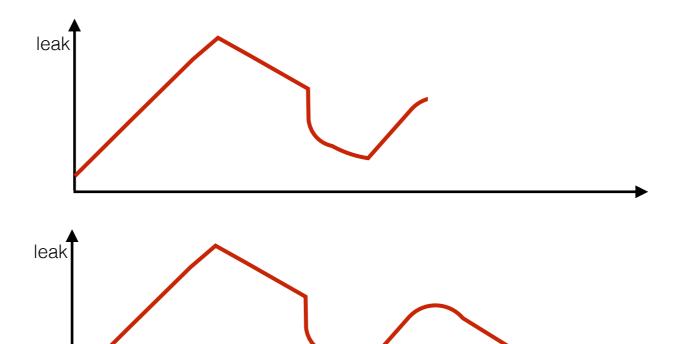

This is particularly relevant for oxide trapped charge (that induces leakage in NMOS) The evolution in time depends **on the energy of the trap and on the temperature**

Leakage current: the net result during a test or in the application depends on temperature and dose rate !

#### **TID (Total Ionising Dose) in CMOS: Summary of Main Concepts**

#### **Summary**

**Devices that are affected by displacement damage in CMOS technologies:**

- photodiodes in Active Pixel Sensors

- diodes or BJTs used for voltage reference generator circuits

- LDMOS (Lateral Diffusion) or Vertical MOS for high-voltage applications

Recent additional observations (whose generality has to be confirmed):

- leakage current between n-wells in the substrate

- non-applicability of the NIEL scaling for DD

#### **Summary**

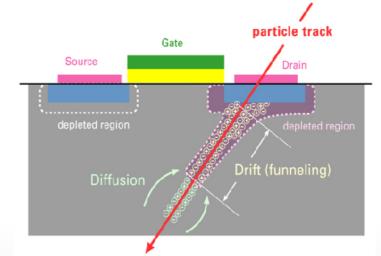

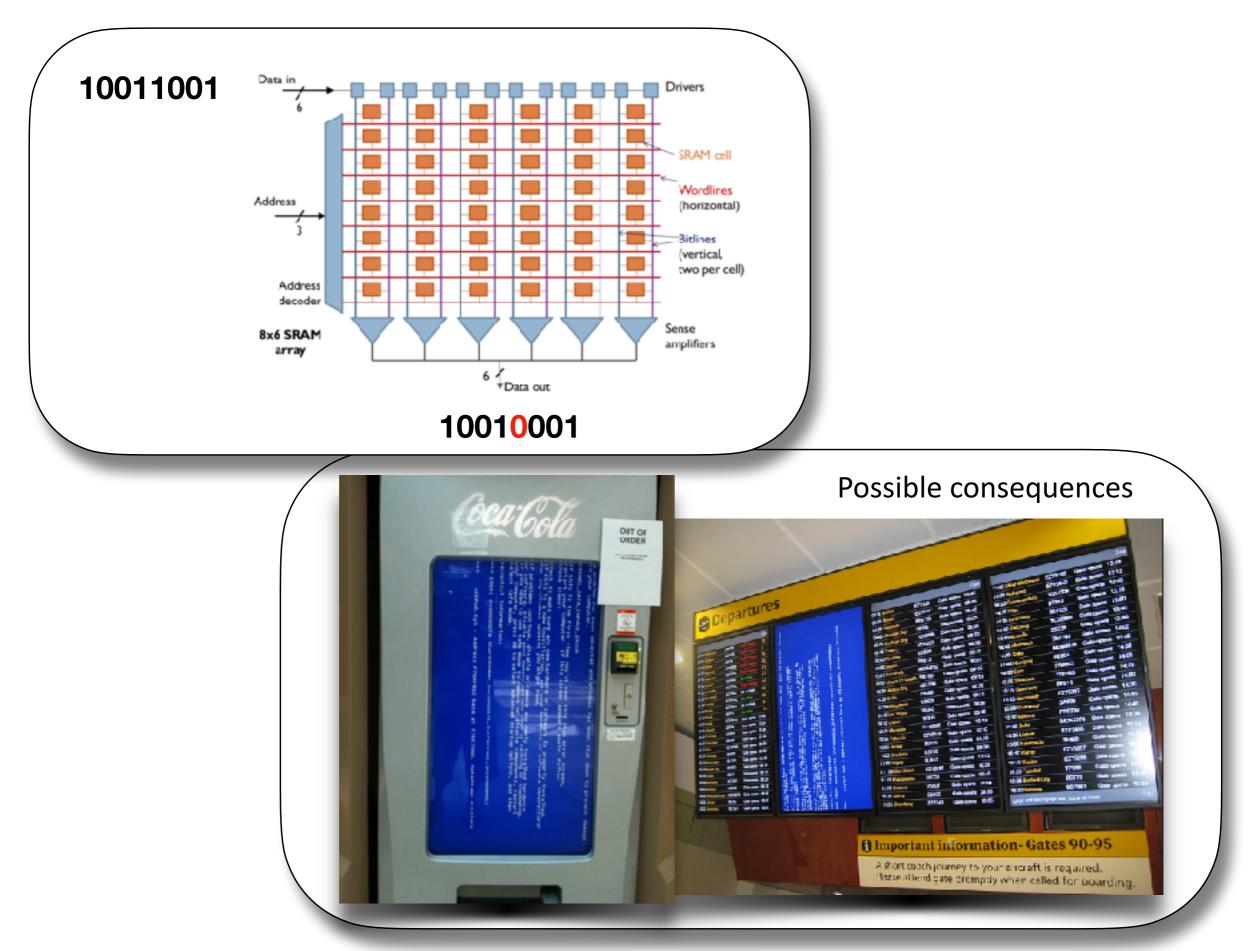

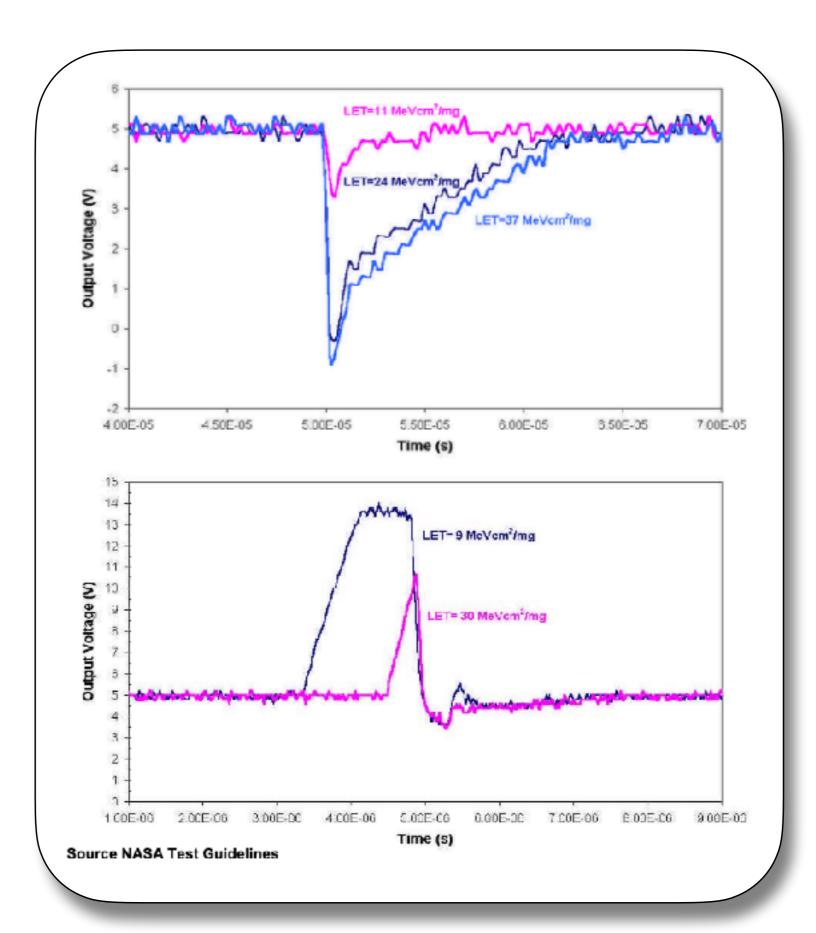

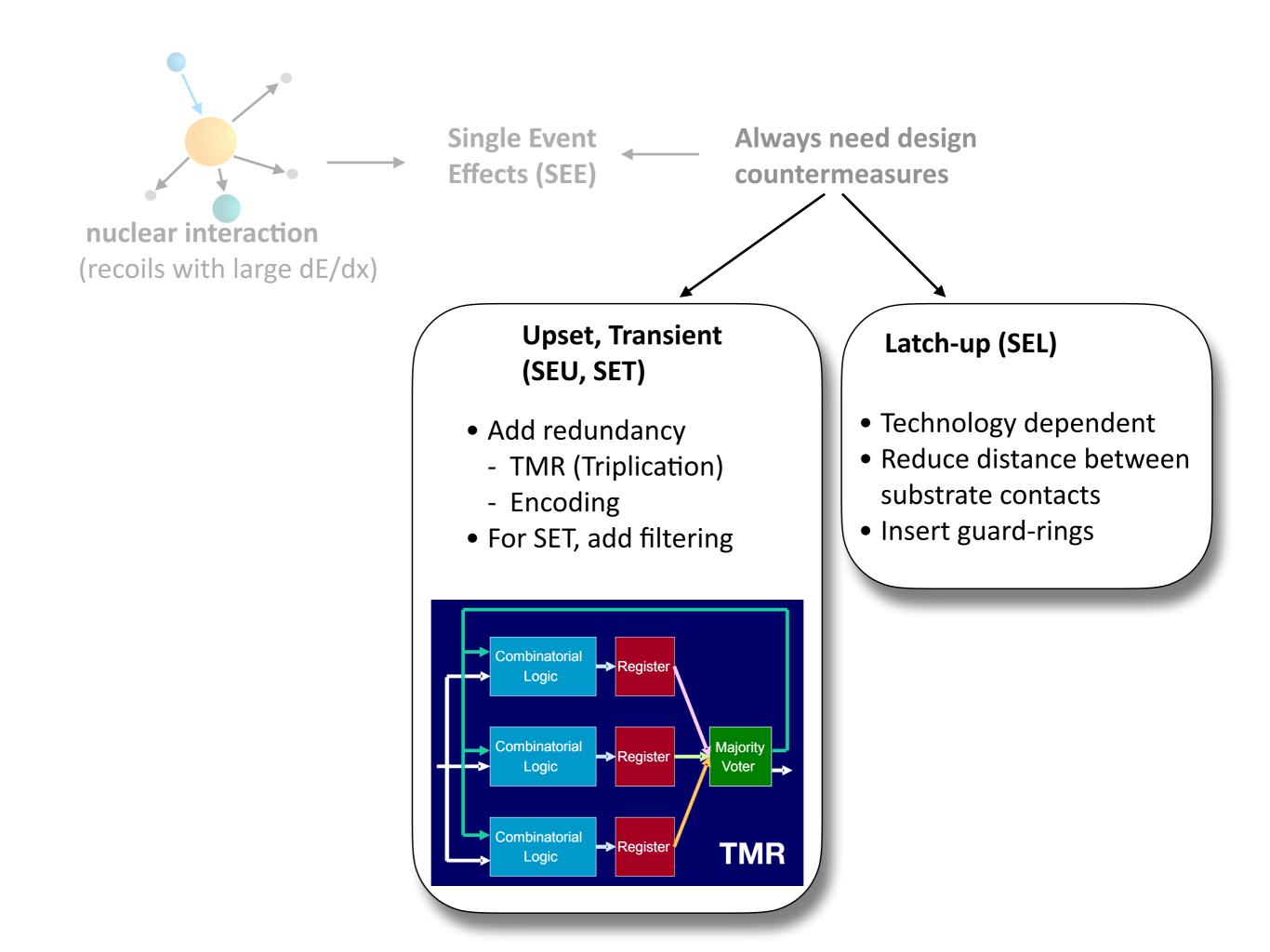

Single Event Effects are due to the instantaneous and local deposition of ionising energy from a single particle

If the deposited charge is sufficient, in CMOS:

Single Event Upset (SEU) Single Event Transient (SET) Single Event Latch-up (SEL) Single Event Upset (SEU): corruption of one bit in a register or memory cell

Single Event Transient (SET): current/voltage pulse that can propagate in the circuit

#### Single Event Latch-up (SEL): turn-on of a parasitic thyristor structure

Latch-up might lead to permanent device damage

Single Event Latchup (SEL) of a high voltage driver for MEMS (vaporized bond wires) After M.O'Bryan et al., "Current Single Event Effects and Radiation Damage Results for Candidate Spacecraft Electronics", NSREC Radiation Effects Data Workshop 2002

## Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

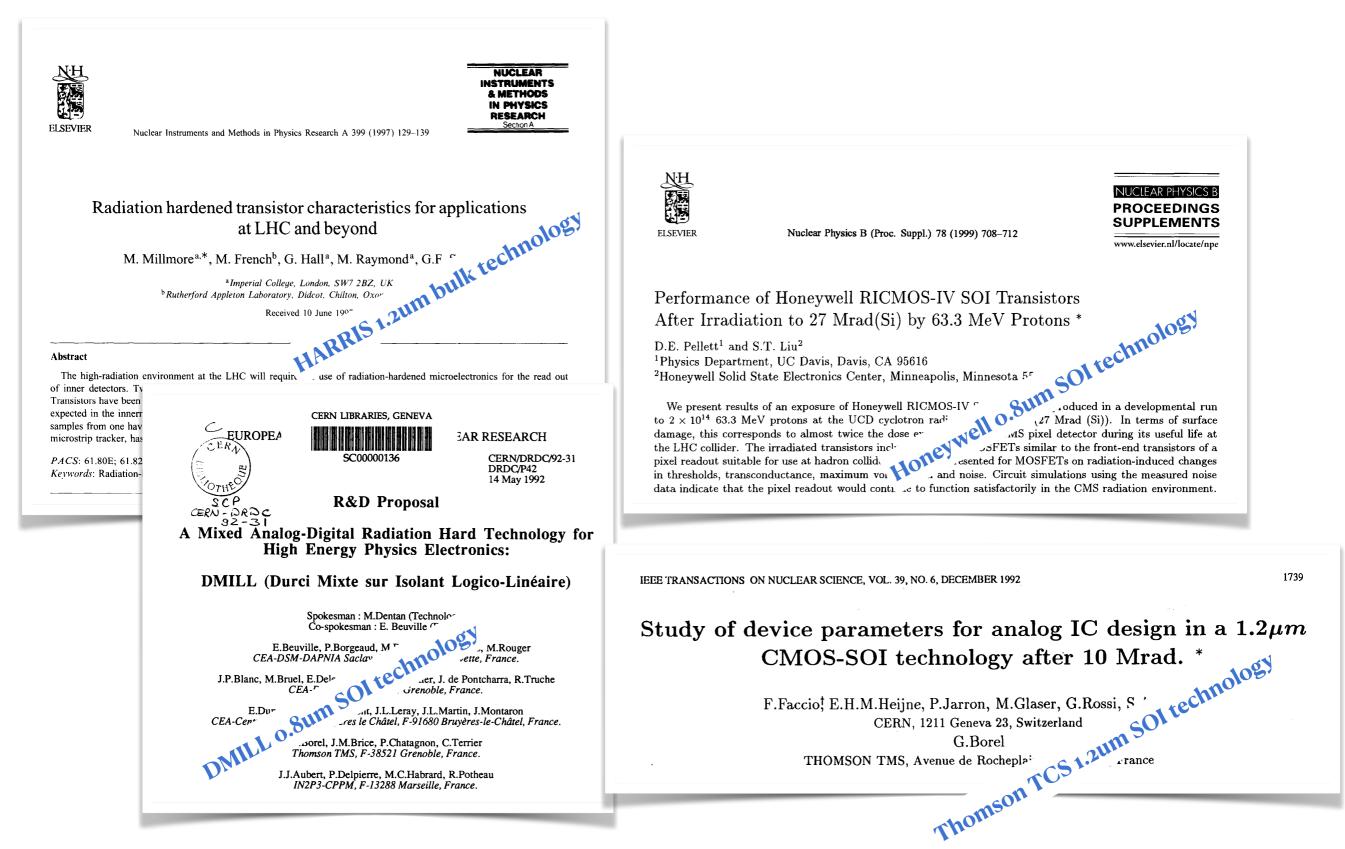

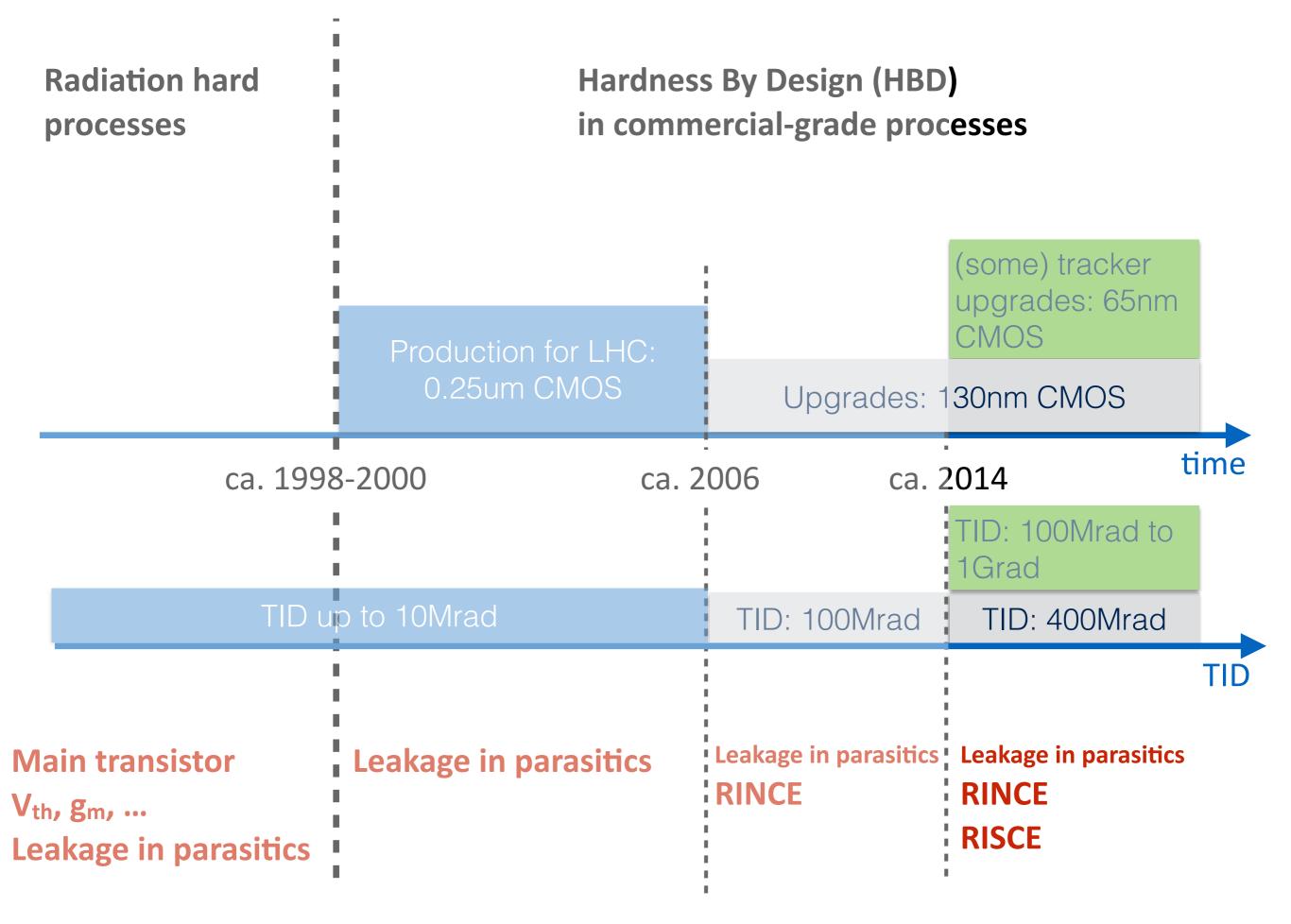

# Radiation-hard ASICs for the development of LHC electronics (ca. 1990-2000)

Dedicated Rad-Hard processes quickly ruled out (only DMILL used in LHC experiments)

#### **Studying radiation tolerance with the tools of the 90s**

Irradiation:

- TID @ CEA Saclay, Pagure

- Neutrons @ CERN PS-ACOL (neutrons from antiproton production target, 3e14 over 2 months)

Measurements:

- Chips packaged in DIL

- Individual transistors manually connected sequentially

- Data saved on floppy disks

- Curves plotted with pencil plotter and interpolated manually to extract the parameters

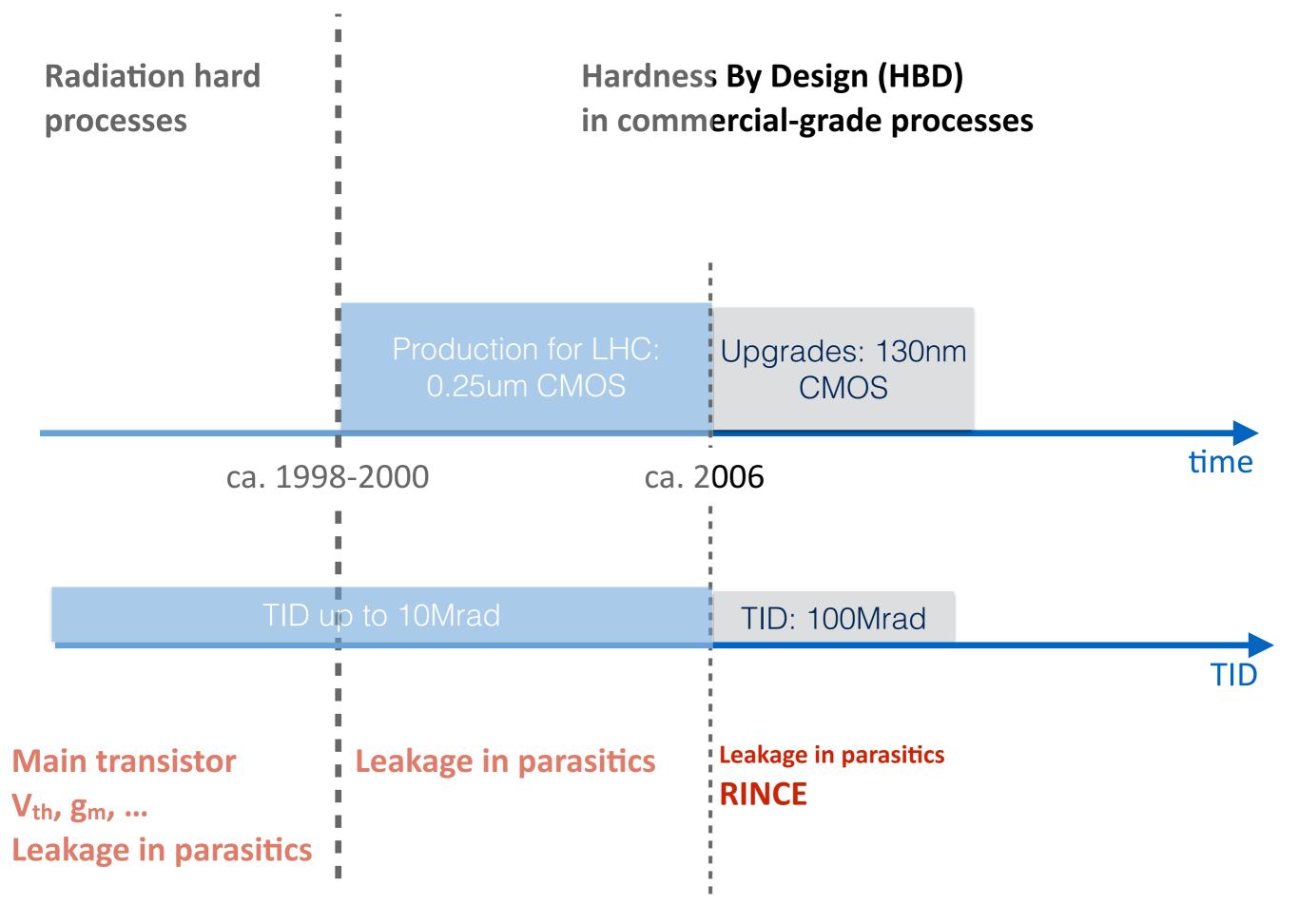

# Radiation-hard ASICs for the development of LHC electronics (ca. 1990-2000)

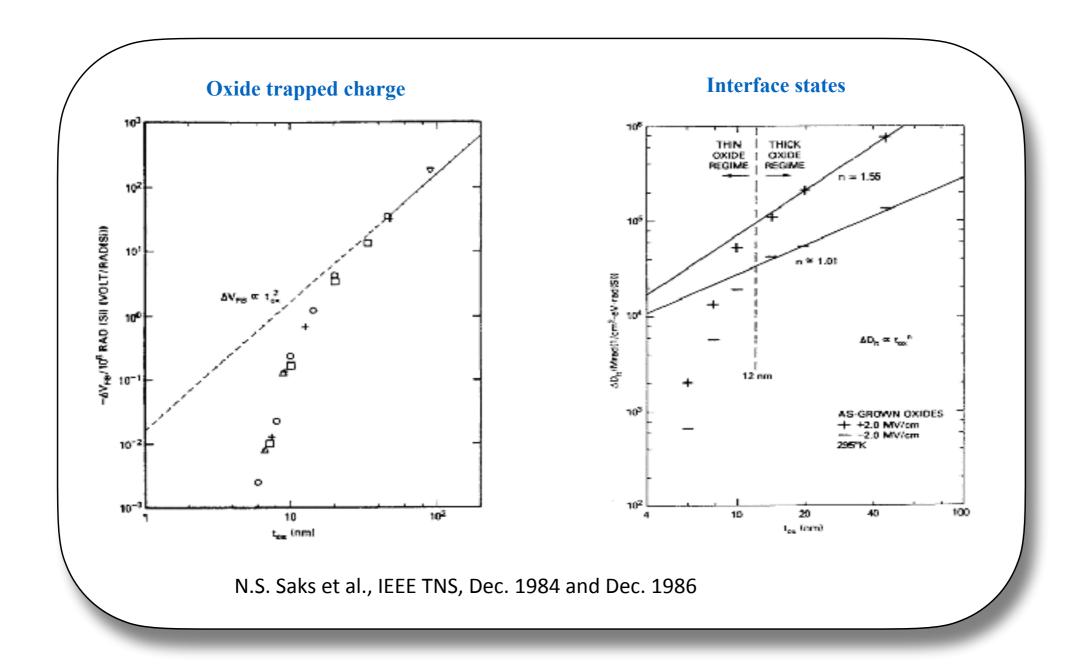

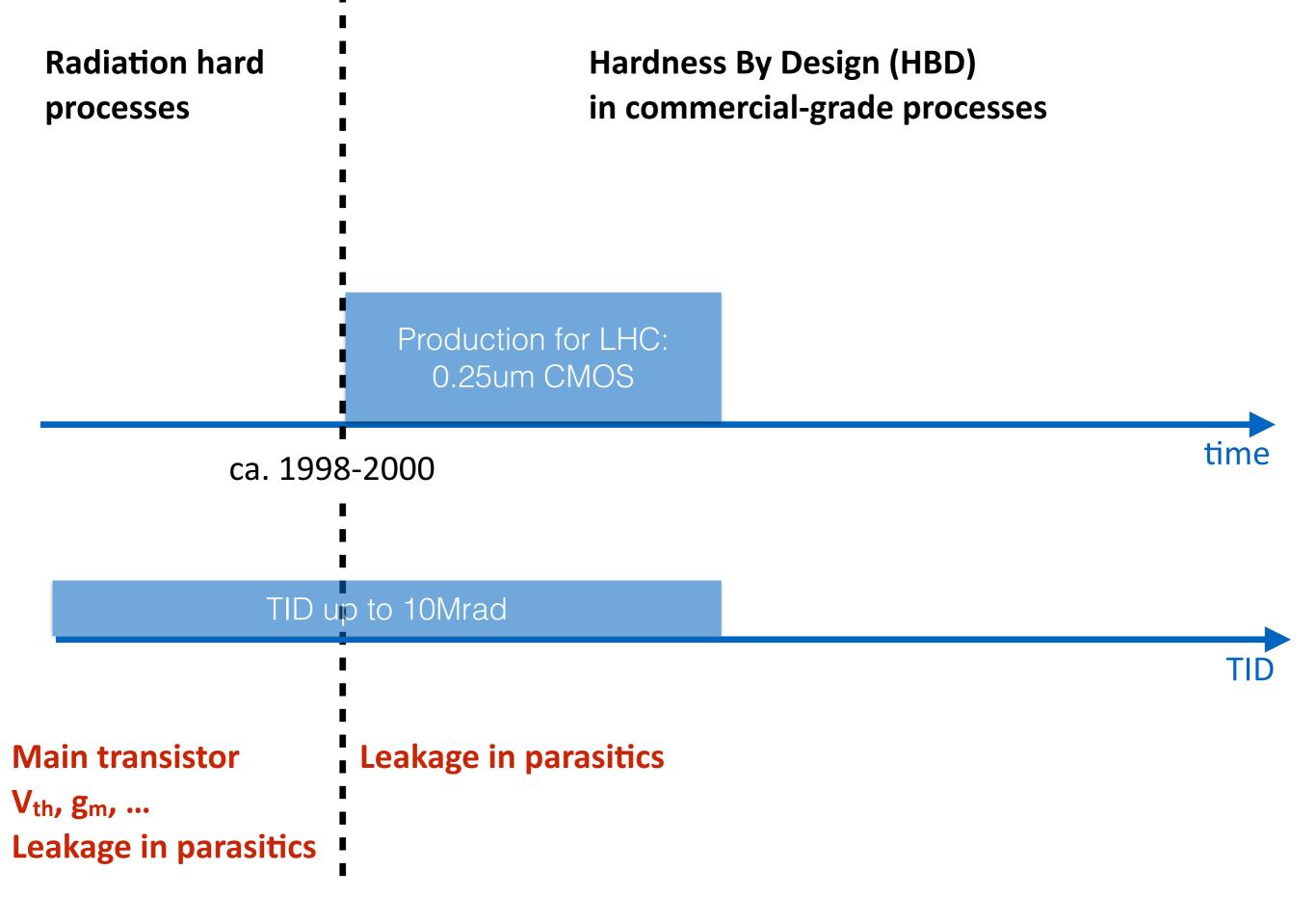

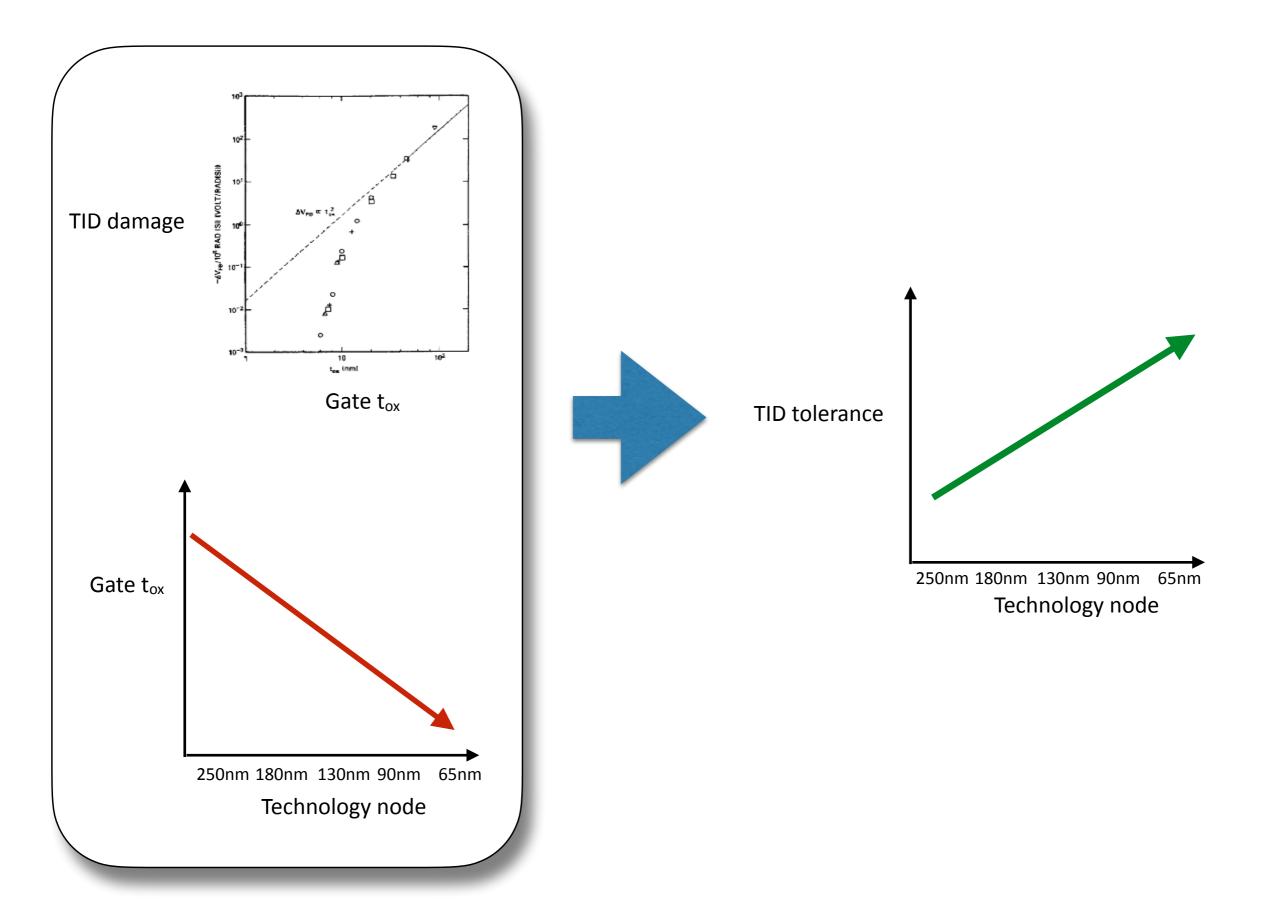

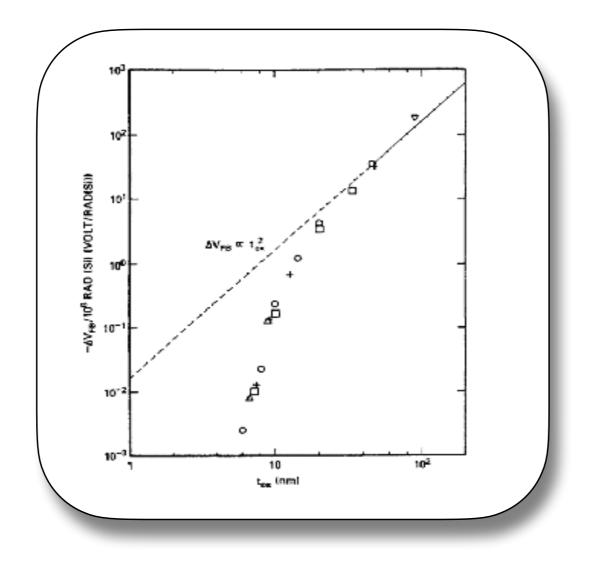

With gate oxides getting thinner than 5-6nm, they became naturally "radiation tolerant" to very high doses

# Radiation-hard ASICs for the development of LHC electronics (ca. 1990-2000)

- With gate oxides getting thinner than 5-6nm, they became naturally "radiation tolerant" to very high doses

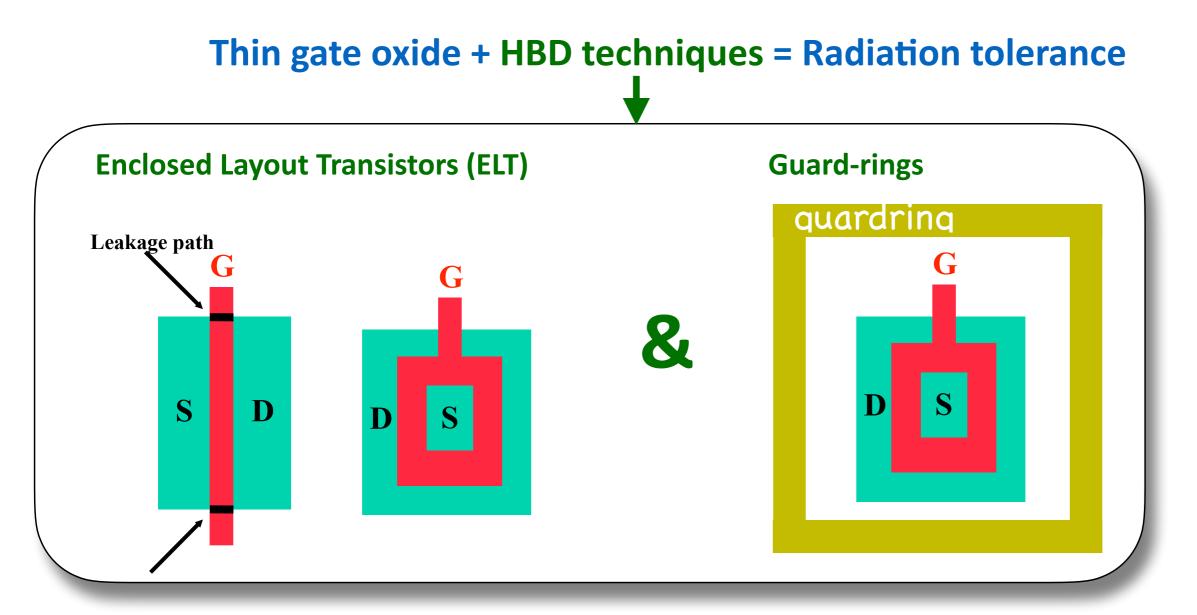

- parasitic oxides (mainly STI) are the main limit to the radiation tolerance

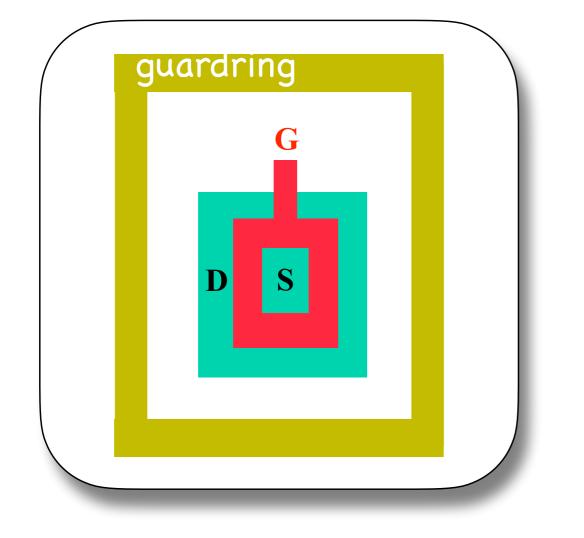

- with the systematic adoption of Hardness-By-Design (HBD) techniques, it is possible to avoid STI-related damage

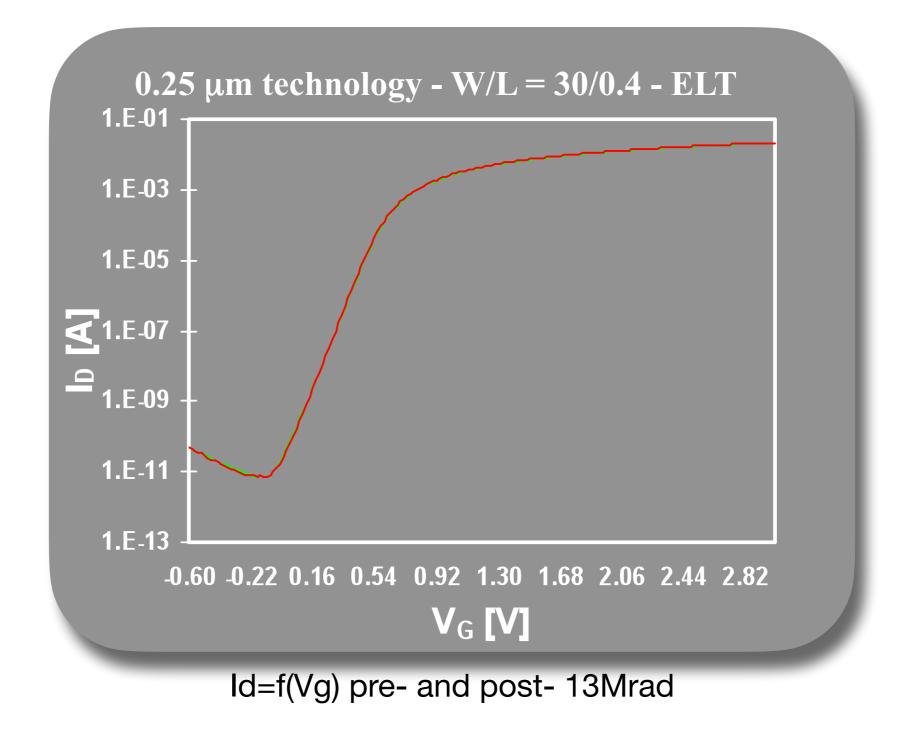

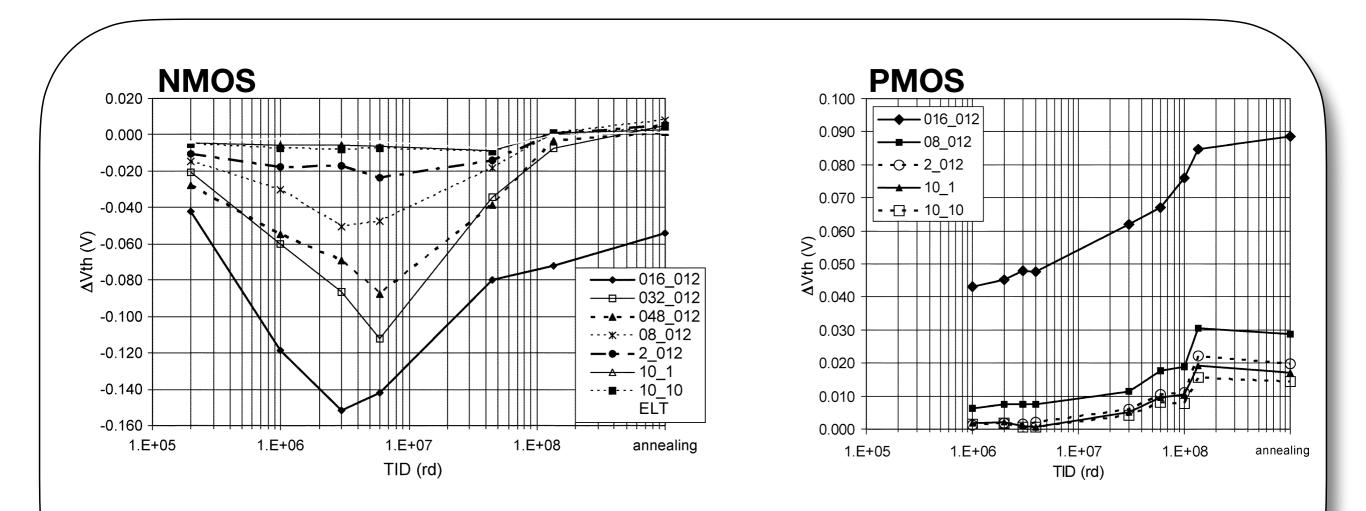

## ELT transistors in 0.25um technology: no relevant TID effects up to 10Mrad

# Radiation-hard ASICs for the development of LHC electronics (ca. 1990-2000)

**Enclosed Layout Transistors (ELT) + Guard-rings**

Most of the ASICs used today in LHC experiments are designed using these techniques in a 250nm CMOS process

This required the development of a dedicated "library" of cells with ELT transistors

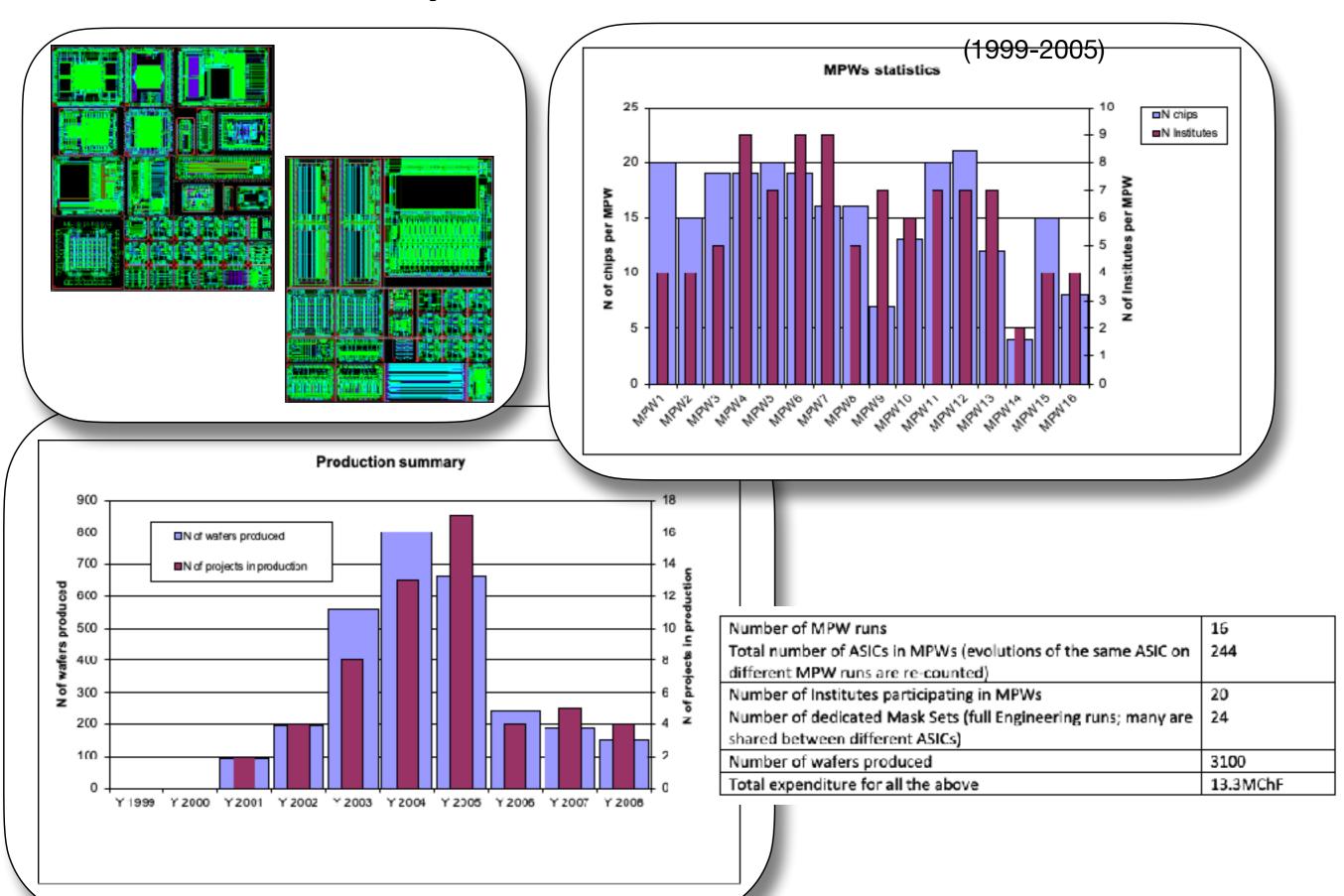

### The CERN "Foundry Service"

## Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

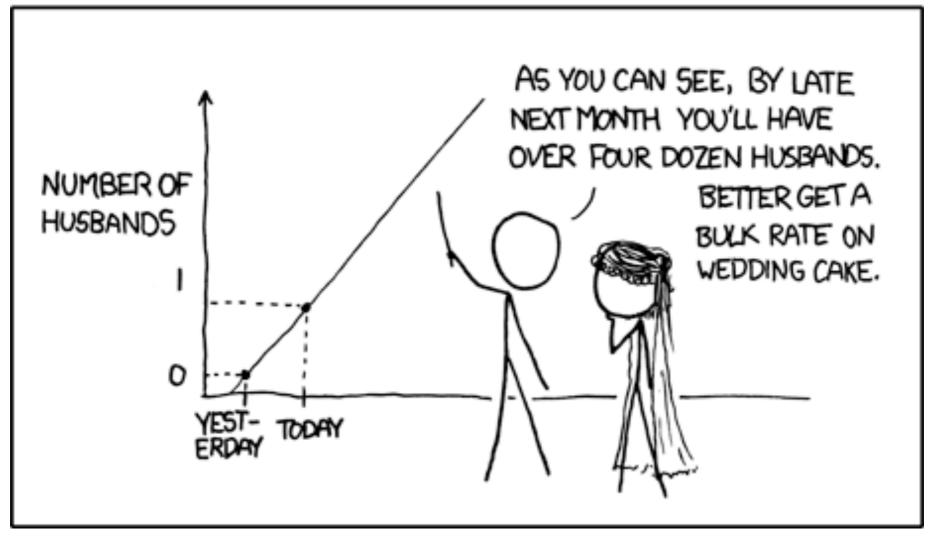

Is this extrapolation correct?

### MY HOBBY: EXTRAPOLATING

#### 2003-2005: study of 130nm node in view of application in LHC upgrades

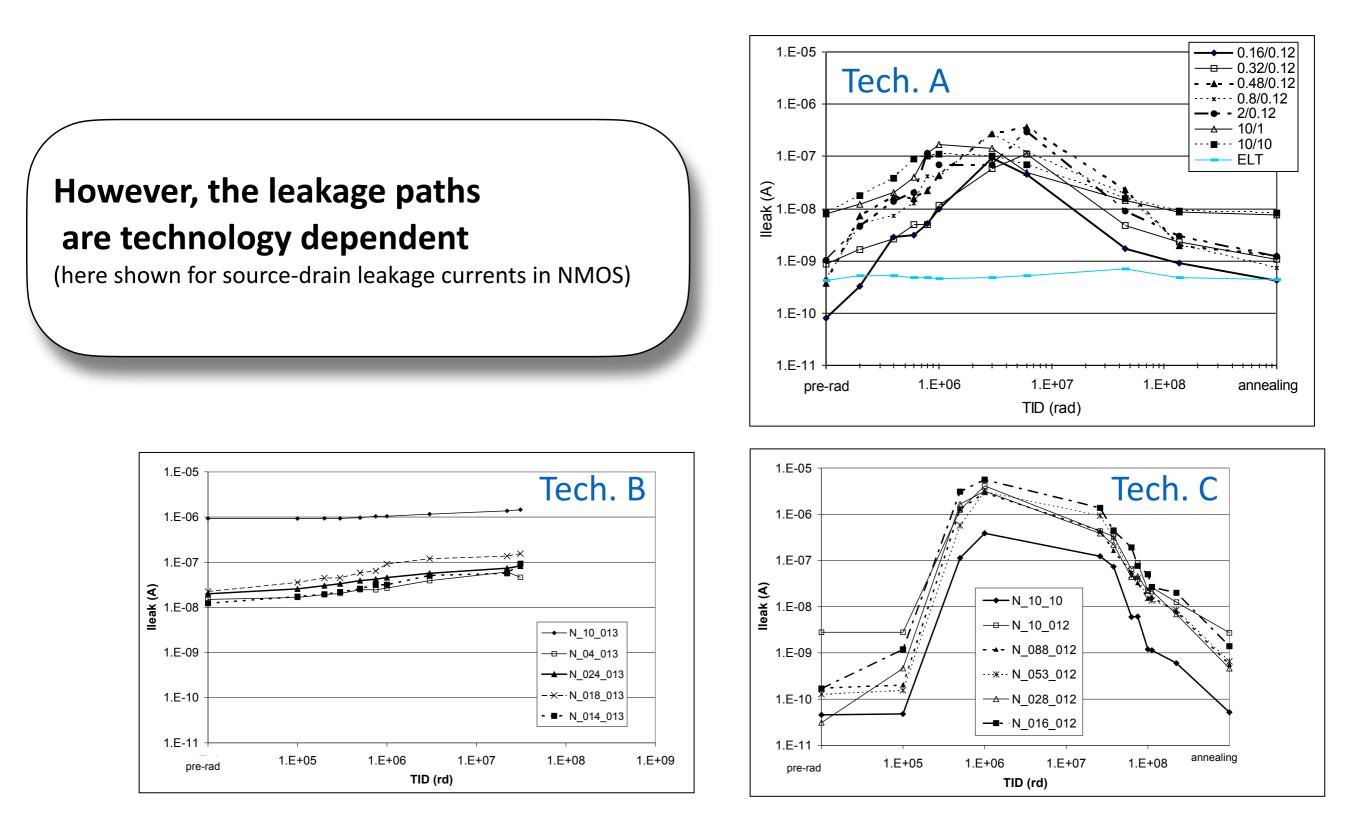

Samples from 3 different vendors were irradiated and measured

The gate oxide in the three 130nm technologies studied appeared to be compatible with applications in environments with multi-100Mrad TID levels

# The selection of the manufacturer (Tech. A) was based on a number of criteria: long-term availability, cost, radiation tolerance, support offering, ...

A large effort was dedicated to the characterisation of the selected technology

Is there still the need for ELTs and guard rings?

No digital library with ELTs and guardrings was developed. The standard cells library from a commercial supplier was considered usable

Designers have to evaluate if the leakage could threaten the circuit/system functionality in the application Flexibility & optimisation of performance BUT It requires system-specific risk assessment

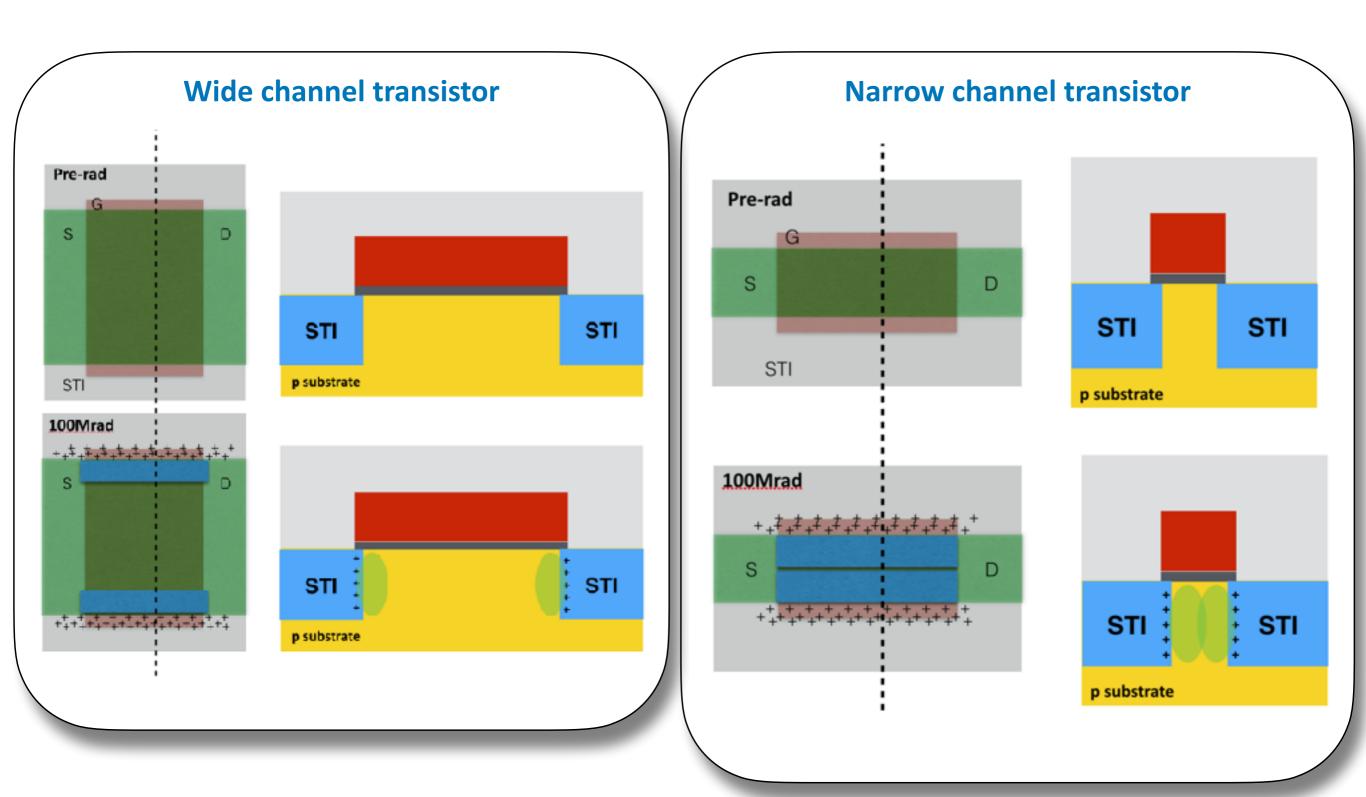

# RINCE (Radiation Induced Narrow Channel Effect): another radiation effect discovered in 130nm technology

This effect has then been observed in all studied technologies in the 350-28nm range

The degradation of the main transistor is W-dependent!

#### **Conceptual representation of the RINCE**

This effects is also traceable to charge trapping in a "parasitic" oxide (STI)

## Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

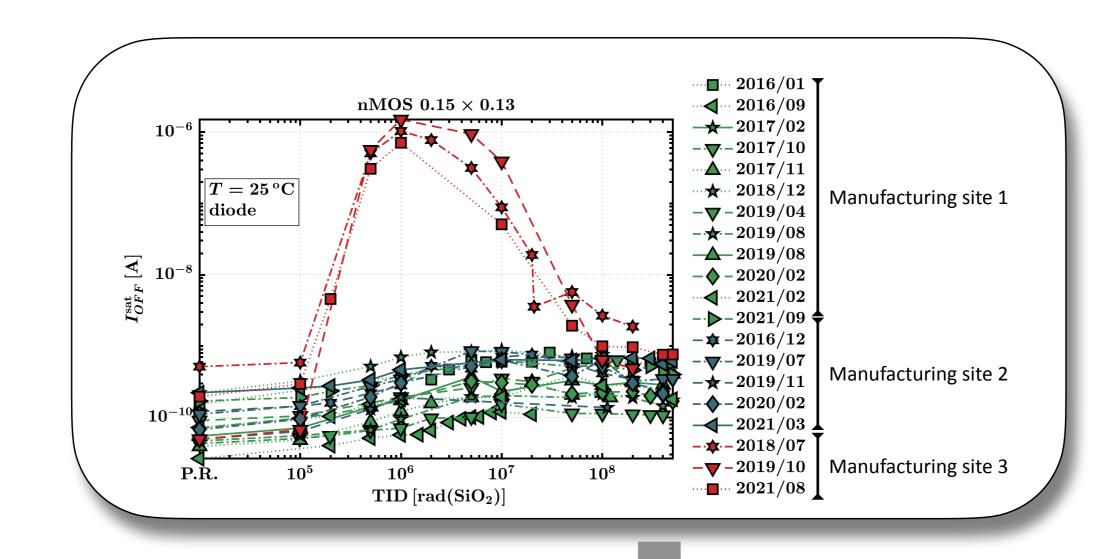

Concerns about long-term availability of the 130nm from "Supplier A" drove the selection of a backup supplier, that gradually has become the main supplier since. **The leakage current evolution in NMOS transistors strongly varies between hardware fabricated in different manufacturing sites (Fabs).**

- Require production in Manufacturing sites 1 and 2 (is it possible?)

- Verify the radiation response of every production run!

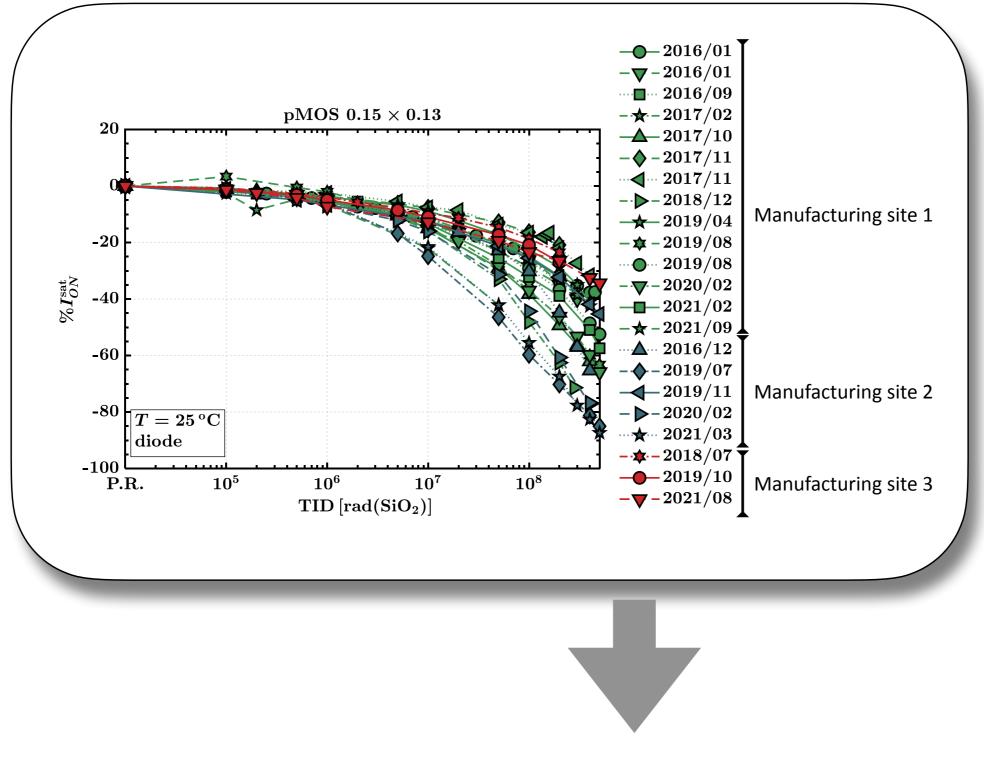

The radiation response of test transistors included in every manufacturing run highlights a relevant lot-to-lot variability at high TID, for PMOS transistors.

- Take design margins to account for this variability in degradation

- Verify the radiation response of every production run!

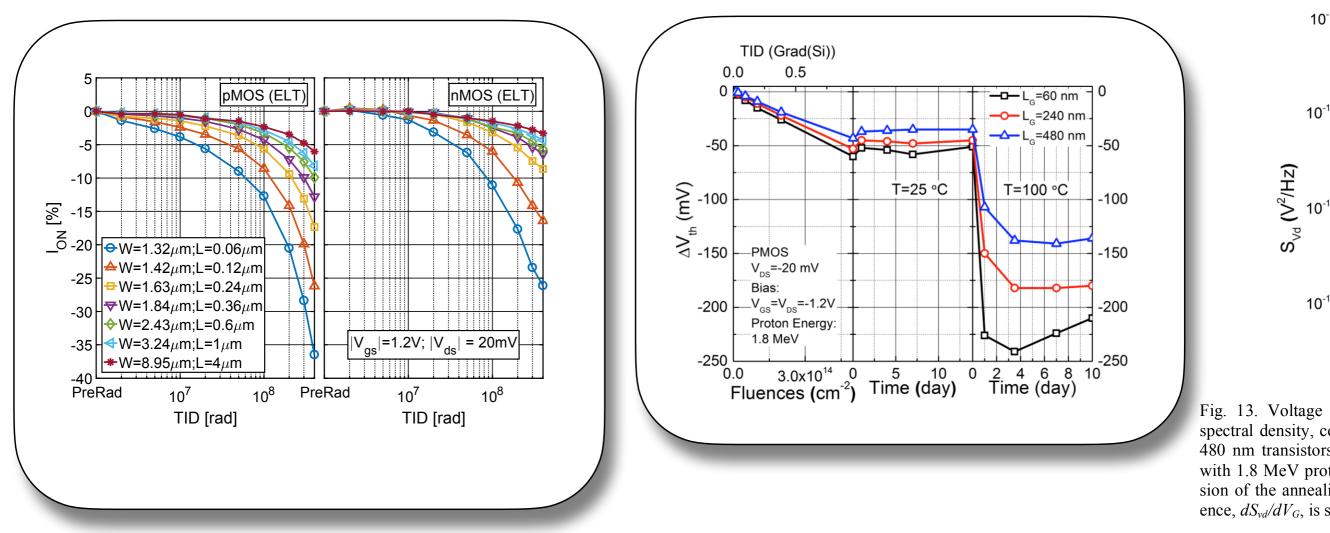

For some HL-LHC detectors, the adoption of the 65nm technology was required. The study of TID effects in transistors revealed the presence of new mechanisms at very high TID levels.

#### **Radiation Induced Short Channel Effect (RISCE)**

S<sub>Vd</sub> (V<sup>2</sup>/Hz)

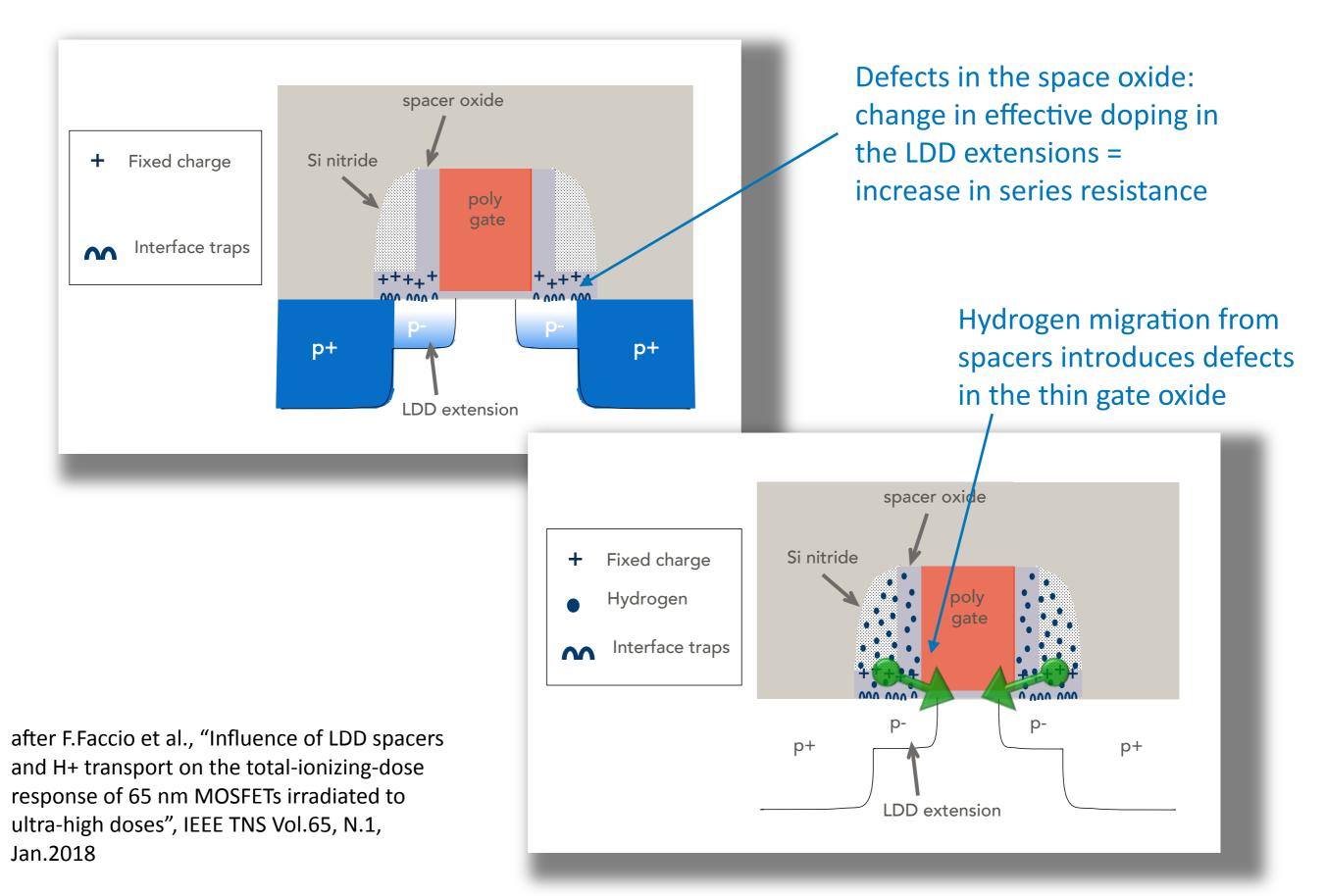

#### The complex mechanisms behind the RISCE is understood Origin: radiation effects in the spacer oxide (another "parasitic" structure)

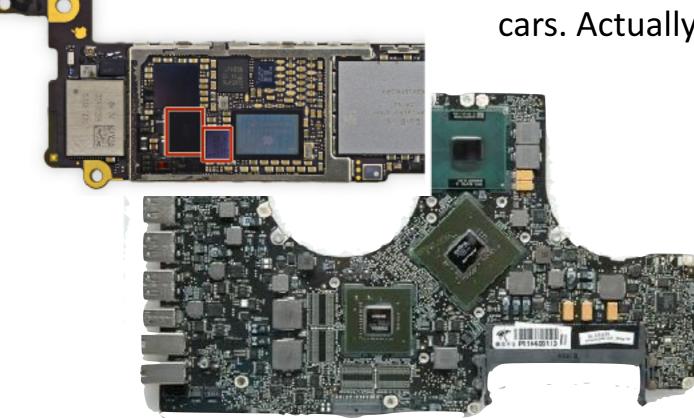

Integrated Circuits are everywhere and their manufacturing requires massive investments

The physics performance of LHC experiments largely relies on ASICs

The reliable functionality of ASICs is threatened by radiation: TID, (displacement damage), SEE

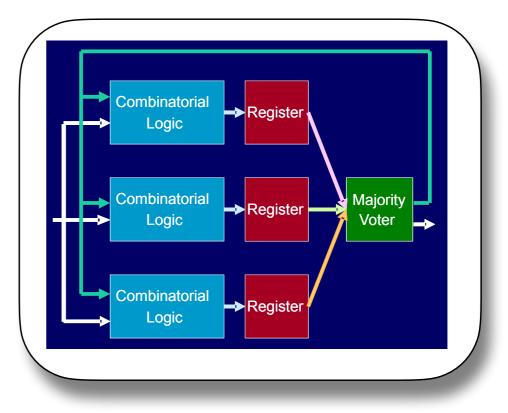

#### ASICs can be made tolerant to radiation using dedicated design techniques: Hardness By Design

(transistor shape like ELT, guard-rings, substrate contacts, transistor size, triplication, encoding, ...)

The thin gate oxide of scaled down CMOS technologies is less sensitive to TID effects.

Parasitic oxides (STI, spacer) dominate the TID response and they particularly affect narrow and short transistors (RINCE, RISCE). This determines a potentially large variability in the radiation response (Fab-to-Fab, lot-to-lot)

Integrated Circuits are everywhere and their manufacturing requires massive investments

The physics performance of LHC experiments largely relies on ASICs

The reliable functionality of ASICs is threatened by radiation: TID, (displacement damage), SEE

ASICs can be made tolerant to radiation using dedicated design techniques: Hardness By Design (transistor shape like ELT, guard-rings, substrate contacts, transistor size, triplication, encoding, ...)

The thin gate oxide of scaled down CMOS technologies is less sensitive to TID effects.

Parasitic oxides (STI, spacer) dominate the TID response and they particularly affect narrow and short transistors (RINCE, RISCE). This determines a potentially large variability in the radiation response (Fab-to-Fab, lot-to-lot)

The radiation levels for HL-LHC electronics are MUCH LARGER than anywhere else. Reliable functionality in this environment is VERY CHALLENGING. Using scaled-down CMOS technologies for ASICs helps, but does not make the job easy.

## Outline

Introduction to ASICs and CMOS technologies Fundamentals of radiation effects Radiation effects in CMOS technologies

A brief history of radiation-tolerant ASIC development for LHC The first generation of LHC experiments: 0.25µm CMOS 130nm CMOS for the upgrades Higher radiation levels for HL-LHC: new effects

**Case Studies**

# Case study 1

# The increase in power consumption in 130nm ASICs

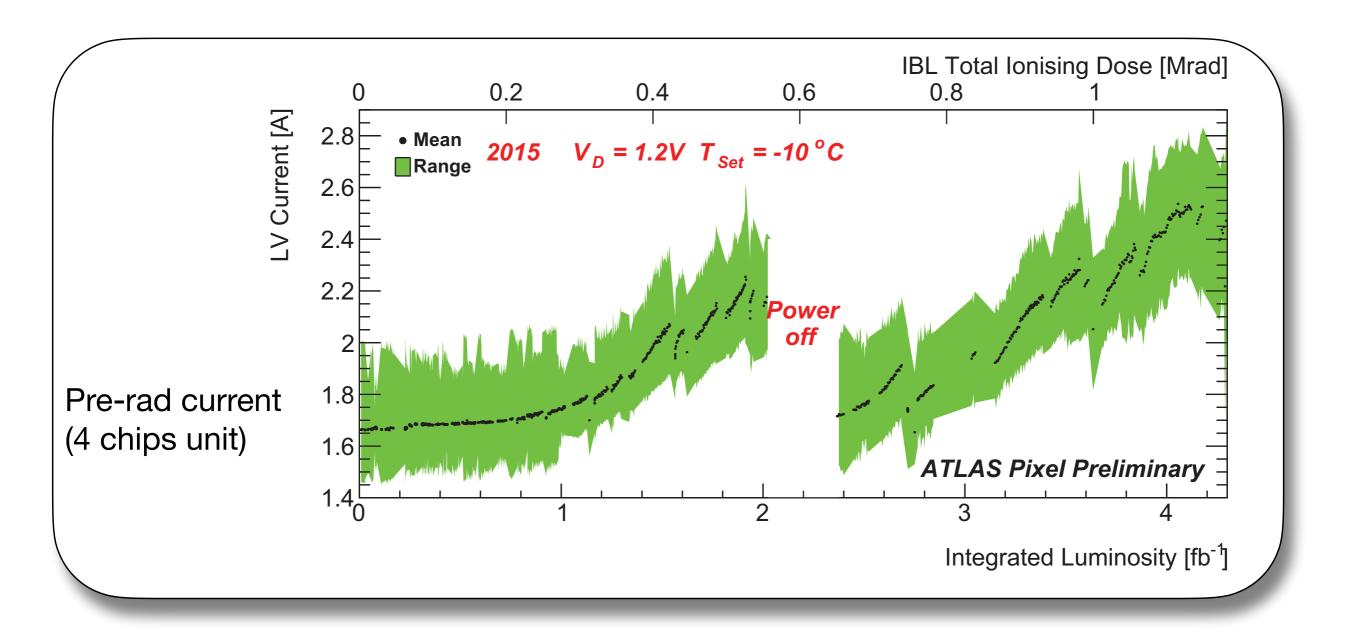

FE-I4 is the readout ASIC for the ATLAS pixel insertable b-layer (IBL) added to the experiment in 2014 and operational since 2015.

Early in its operational life, it showed an increase in the current consumption requiring a power off...

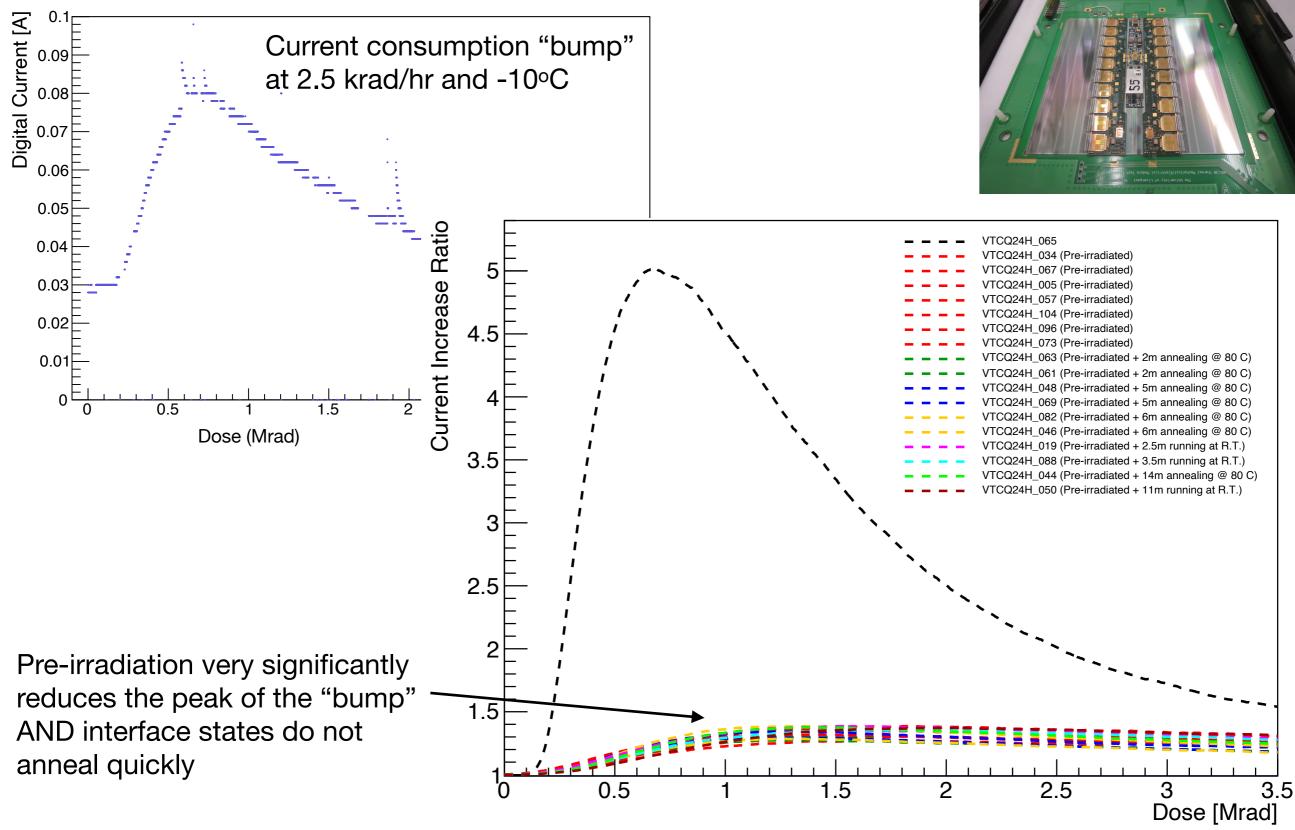

The increase of the power consumption is due to radiation-induced leakage current in the FE-I4 ASIC, strongly dependent on temperature and dose rate

Images from: A.La Rosa, "Irradiation induced effects in the FE-I4 front-end chip of the ATLAS IBL detector", IEEE NSS 2016

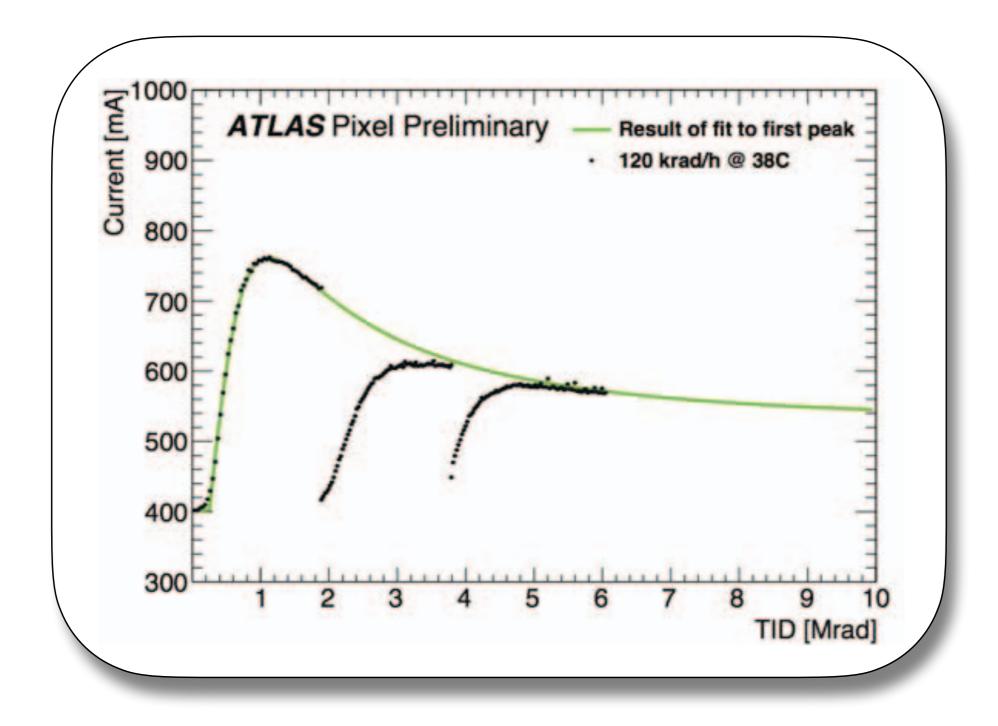

The alternation of irradiation and annealing produces consecutive "bumps" of smaller peak amplitude, suggesting that an attenuation of the problem occurs when sufficiently large TID has accumulated

On the basis of our understanding of the mechanisms leading to the leakage current, the following scenario is plausible for discontinuous irradiation tests

**Irradiation**

#### **Solution in ATLAS pixels**

- rise the temperature of the detector (as much as compatible with safe operation)

- patiently wait until the TID brings the chips after the "TID bump"

but in general, we can think the accumulation of sufficient TID to be a possible strategy to avoid the appearance of a large "bump" in the current consumption

Warning: temperature and dose rate play a key role, and the strategy can only work IF <u>interface states do not significantly anneal</u> at the operational temperature

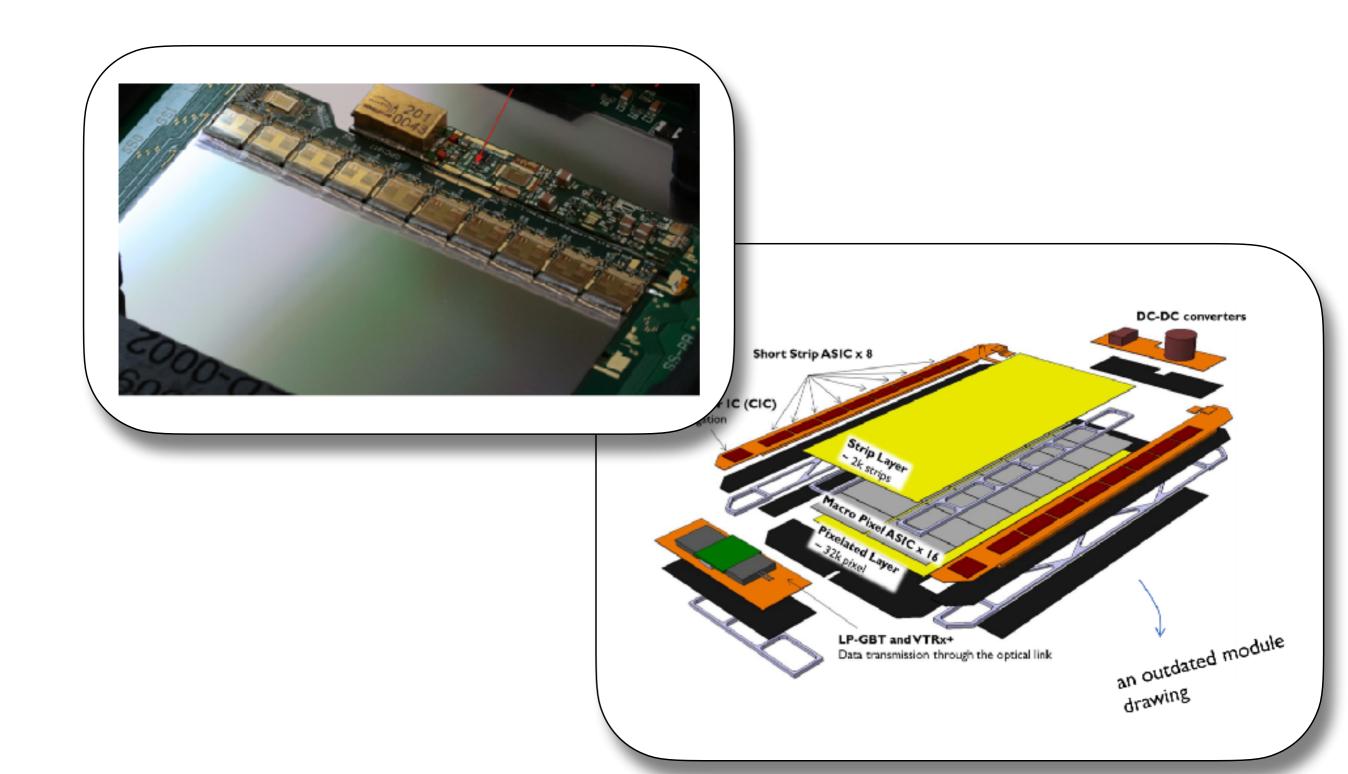

# Example where the pre-irradiation strategy is used: the ABCstar readout ASIC for the ATLAS HL-LHC inner tracker (strip detector).

Images from: L.Poley et al., "The ABC130 barrel module prototyping programme for the ATLAS strip tracker", 2020 JINST 15 P09004

# Case study 2

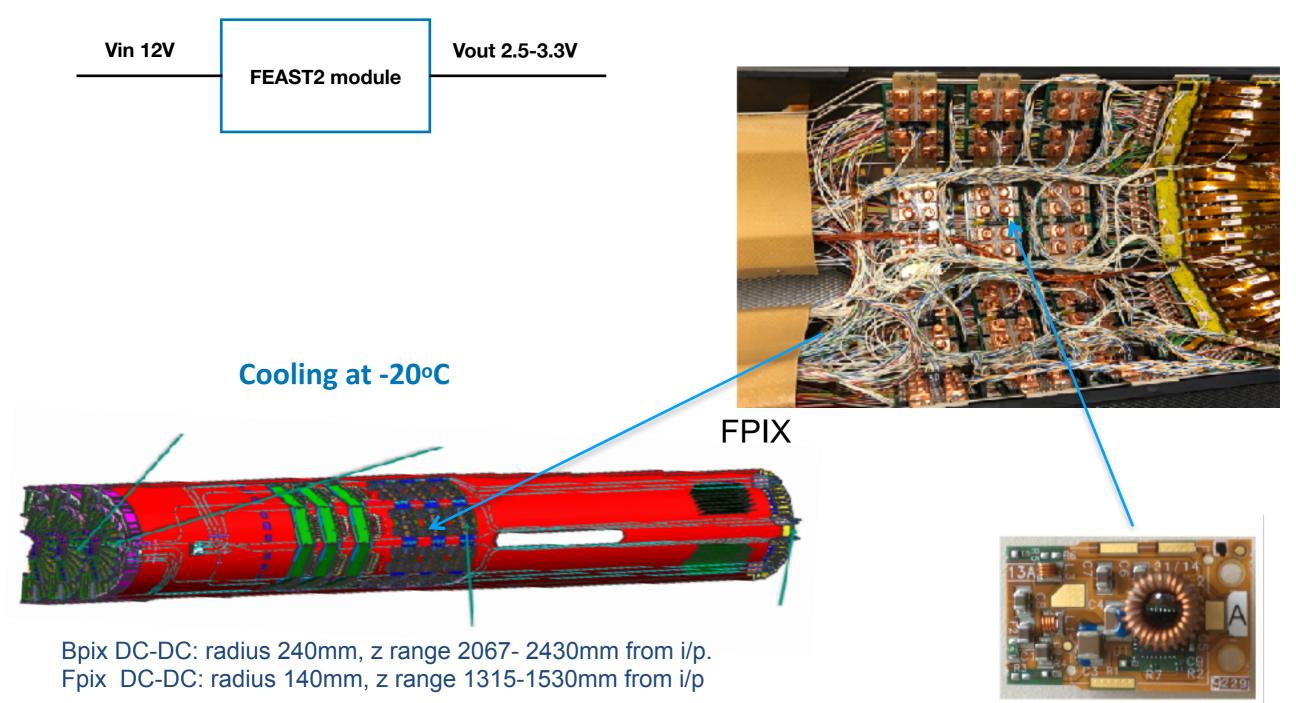

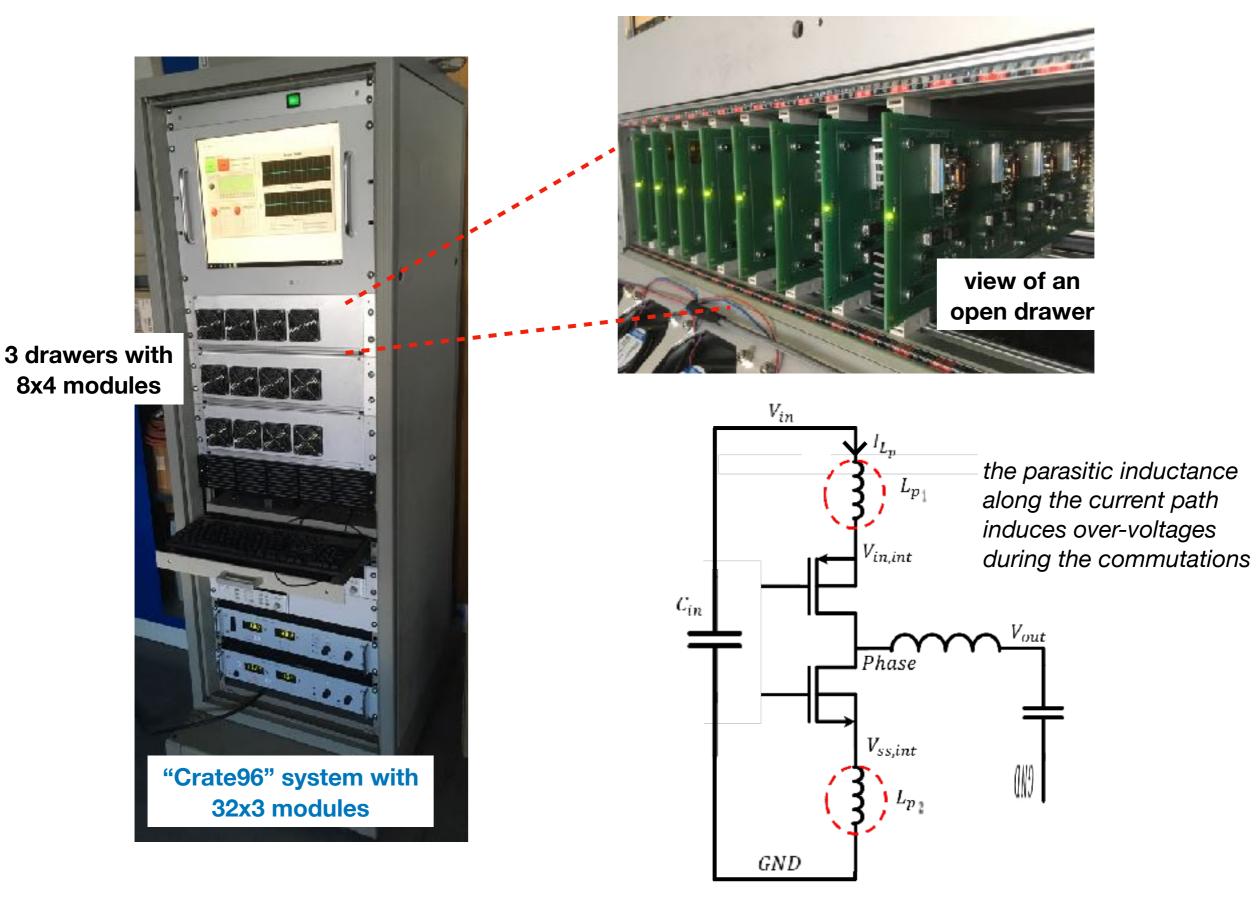

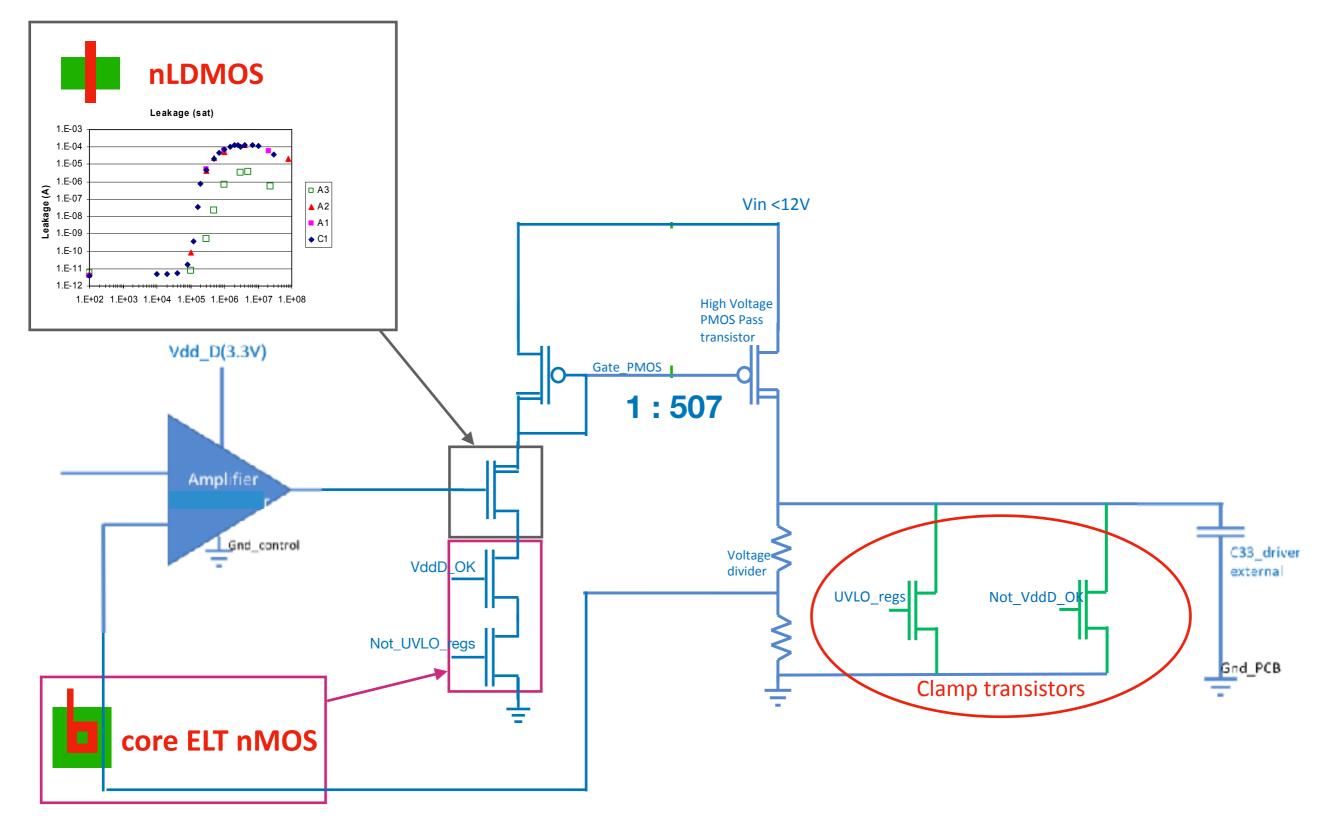

# The lonely perpetrator in the DCDC FEAST2 case

How an individual transistor threatened the operation of the CMS pixel detector

Investigation = the act or process of examining a crime, problem, statement, etc. carefully, especially to discover the truth

### The crime scene

### **FEAST2** in the CMS pixel detector

## Witnesses

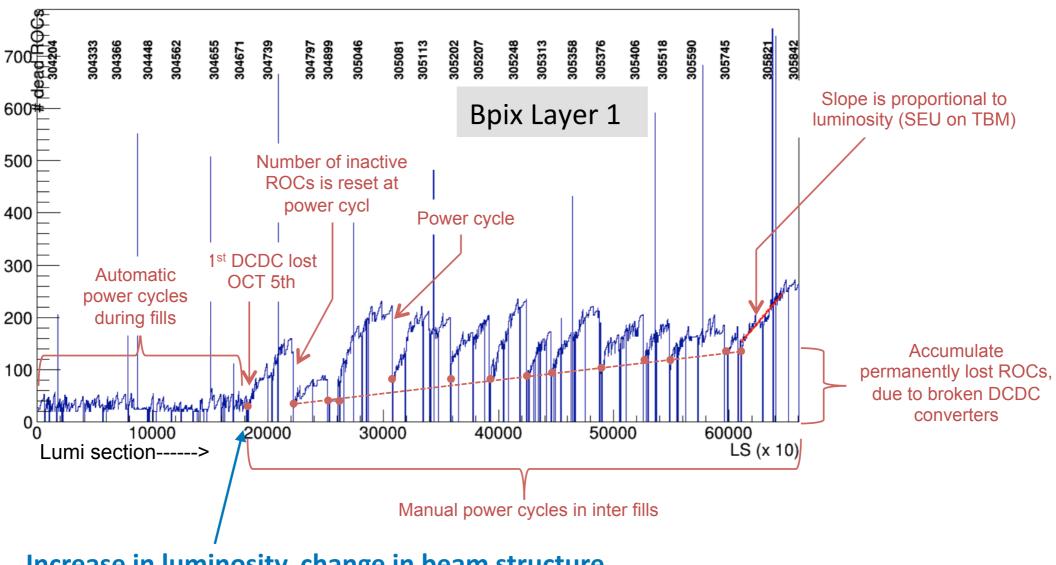

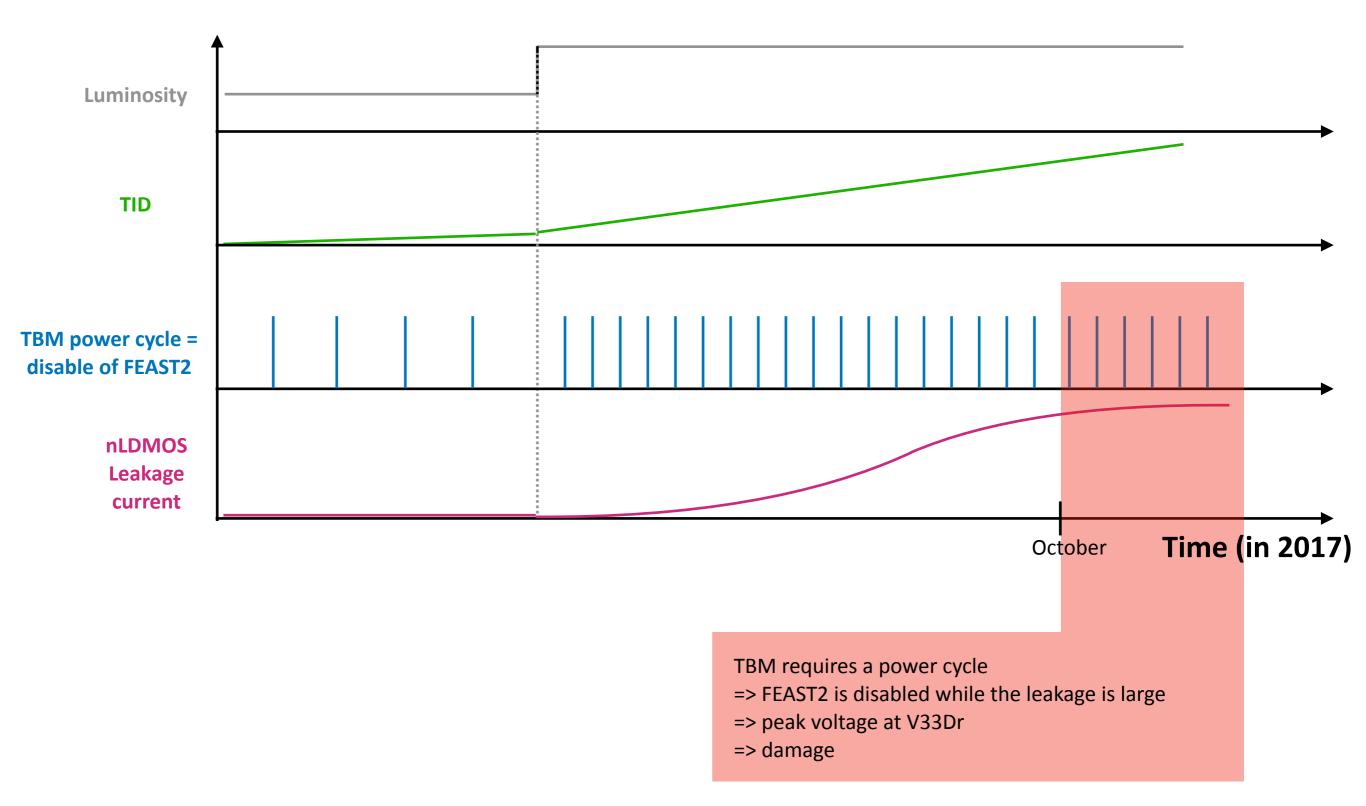

## Failure of FEAST DCDCs in the CMS pixel detector

Increase in luminosity, change in beam structure

#### No correlation with:

DCDCs fail during disable/enable cycles

- output voltage

- output current

- position in the detector

- anything other than the beam

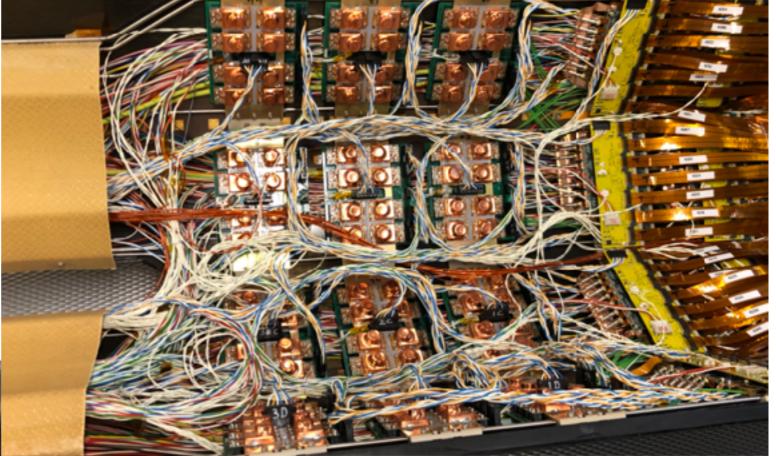

#### Plan around November 2017

**Rest of 2017 Physics Run**

Nothing can be done. Accept loss of modules

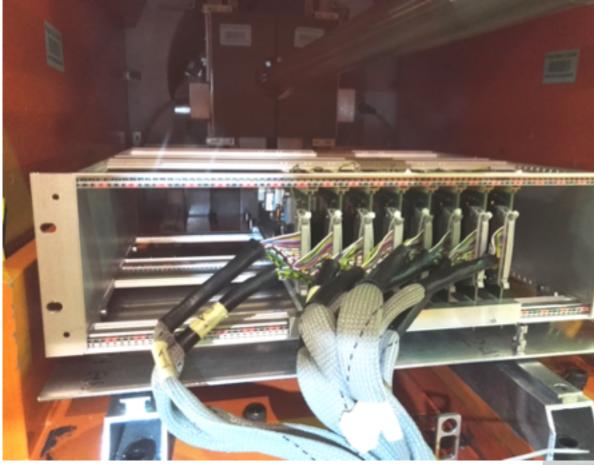

**YETS 17-18**

Request longer Year-End Stop Open the detector Extract all DCDC modules Replace (all?) modules (fuse changed)

2018 Physics Run

Find a patch ensuring data taking

LS2

Solve the problem for the long term

#### T "At this pace, game over for CMS around May 2018"

87

## The autopsy

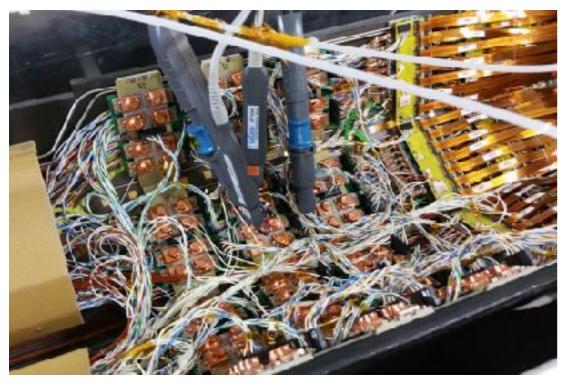

## YETS 17-18: Merry Christmas!

#### Photo memories from the 2017 Christmas Break

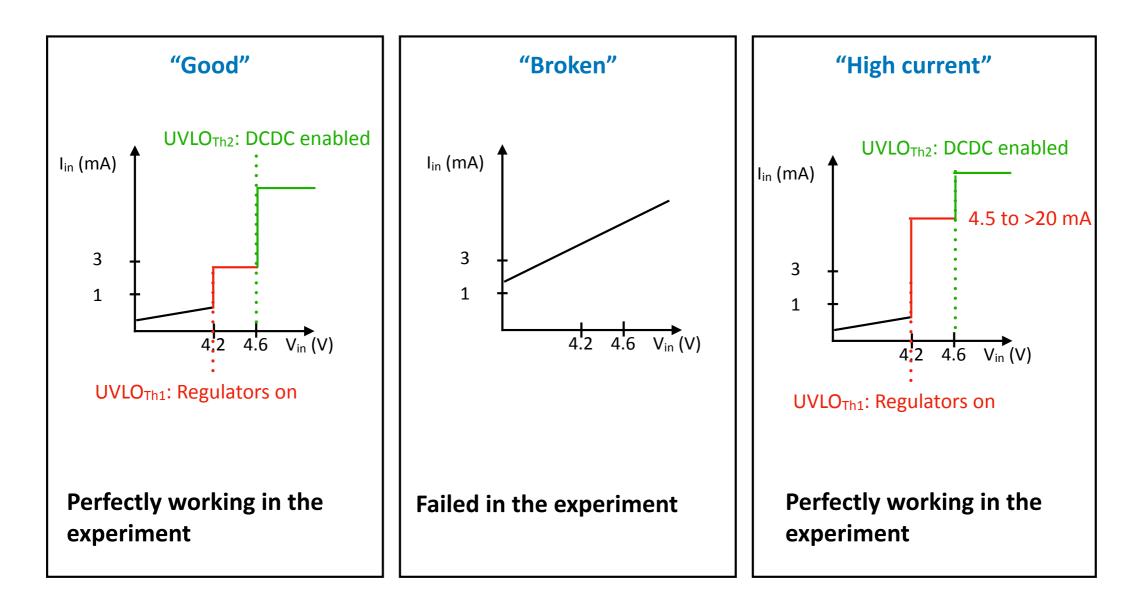

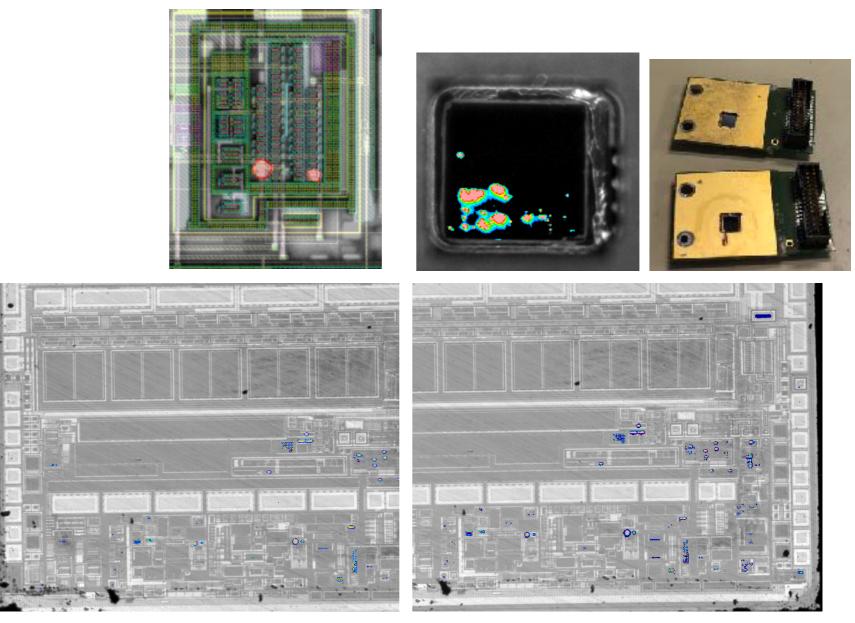

# FEAST2 modules in the CMS experiment were found to present 2 distinct types of damage

Perfectly working in the system but found to have anomalous current when tested

- "Broken" samples failed to provide any output voltage

- "High-current" samples were perfectly functional, but were found to have an excessive current below UVLO

| U                               |             | Number of  |               | /<br>Tested working with | Tested working         | BROKEN            | HIGH CURRENT  |

|---------------------------------|-------------|------------|---------------|--------------------------|------------------------|-------------------|---------------|

|                                 | Pixel Names | Converters | Tested Broken | High Current             | with normal<br>current | % with respect to |               |

|                                 |             | TOTAL      | "BROKEN"      | "HIGH CURRENT"           | "GOOD"                 | total             | total working |

| BPIX (+Z, Near)                 | BPIX-Bpl    | 208        | 4             | 48                       | 156                    | 1.9               | 23.5          |

| BPIX (-Z, Near)                 | BPIX-BmI    | 208        | 10            | 48                       | 150                    | 4.8               | 24.2          |

| BPIX (+Z, Far)                  | BPIX-BpO    | 208        | 13            | 70                       | 125                    | 6.3               | 35.9          |

| BPIX (-Z, Far)                  | BPIX-BmO    | 208        | 11            | 70                       | 127                    | 5.3               | 35.5          |

| FPIX (+Z, Near)                 | FPIX-BpI    | 96         | 7             | 41                       | 48                     | 7.3               | 46.1          |

| FPIX (-Z, Near)                 | FPIX-BmI    | 96         | 7             | 34                       | 55                     | 7.3               | 38.2          |

| FPIX (+Z, Far)                  | FPIX-BpO    | 96         | 9             | 23                       | 64                     | 9.4               | 26.4          |

| FPIX (-Z, Far)                  | FPIX-BmO    | 96         | 6             | 22                       | 68                     | 6.3               | 24.4          |

| BPIX - not connected to modules |             | 32         | 2             | 8                        | 22                     | 6.3               | 26.7          |

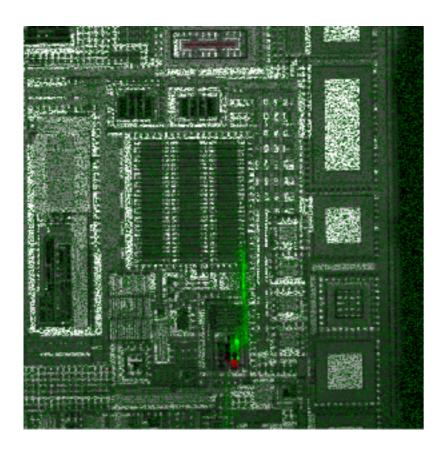

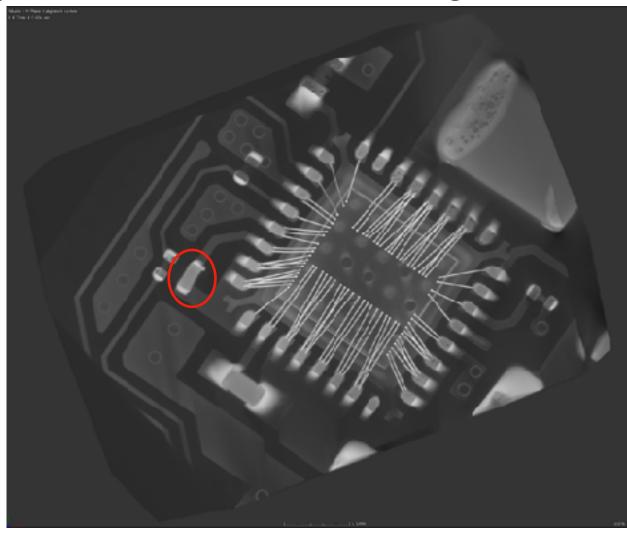

# Failure Analysis (FA) with emission microscopy and Optical Beam Induced Resistance Change (OBIRCH) at MASER (NL)

During OBIRCH a laser beam selectively illuminates the metal lines, altering their resistance. The consequent input current change is measured, allowing the mapping of current paths. In broken FEAST2 samples, current flows to the clamp transistors.

Emission images are based on the detection of photons generated from hot carriers (therefore only conducting NMOS transistors are well visible). "Broken" or "High-current" FEAST2 samples showed different current paths.

#### Observations match the hypothesis that one of the two on-chip clamp transistors is damaged

## The motive

Why the clamp transistor(s) is(are) damaged?

Flawed ASICs?

Flawed PCBs?

**Radiation in ASIC?**

EM noise?

**Radiation in package?**

**Environmental conditions?**

**Electrical stress?**

**Combination of any of the above??**

#### **Environmental conditions?**

Test in a 3T magnetic field revealed no problem

#### Flawed PCBs?

Faulty capacitor, or intermittent contacts of the capacitor in the PCB generated a stress that produced somewhat similar damage

Cap removed

3D X-ray imaging of the module to inspect the quality of the soldering of the capacitor to the PCB

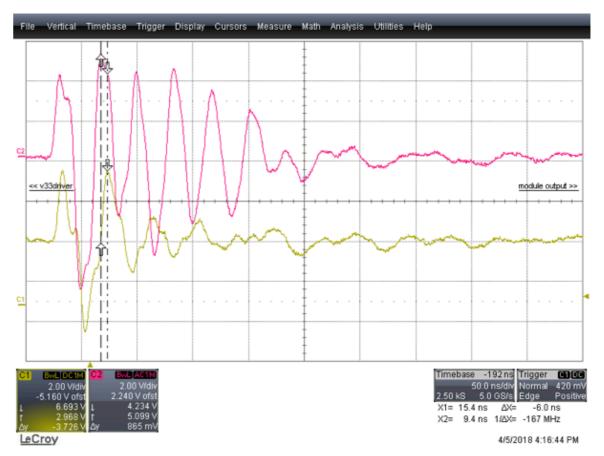

~9.1V ~7.3V Measure P1:mean(C1) P2:max(C2) P3:max(C4) P4:max(C3) P5:freq(C4) P6:freq(C3) 3.616 V 37 mV 45 mV 220 mV 385.4 MHz value 459.1 MHz status 694.0 ns -633.2 ns 60.8 ns 1/ΔX= -1.5793 MHz LeCroy 1/15/2018 9:43:51 AM

Vertical Timebase Trigger Display Cursors Measure Math Analysis Utilities Help

Waveform of the V33Dr node when the capacitance has intermittent contacts to the PCB

#### **Electrical stress?**

Long-term ageing tests on 124 converters did not reveal problems with FEAST2 ASICs

#### **EM noise? Environmental conditions?**

# Injection of EM noise by capacitive coupling to the input/output and signal lines. The converter appears to be very resilient

Led by F. Szoncso and D. Valuch

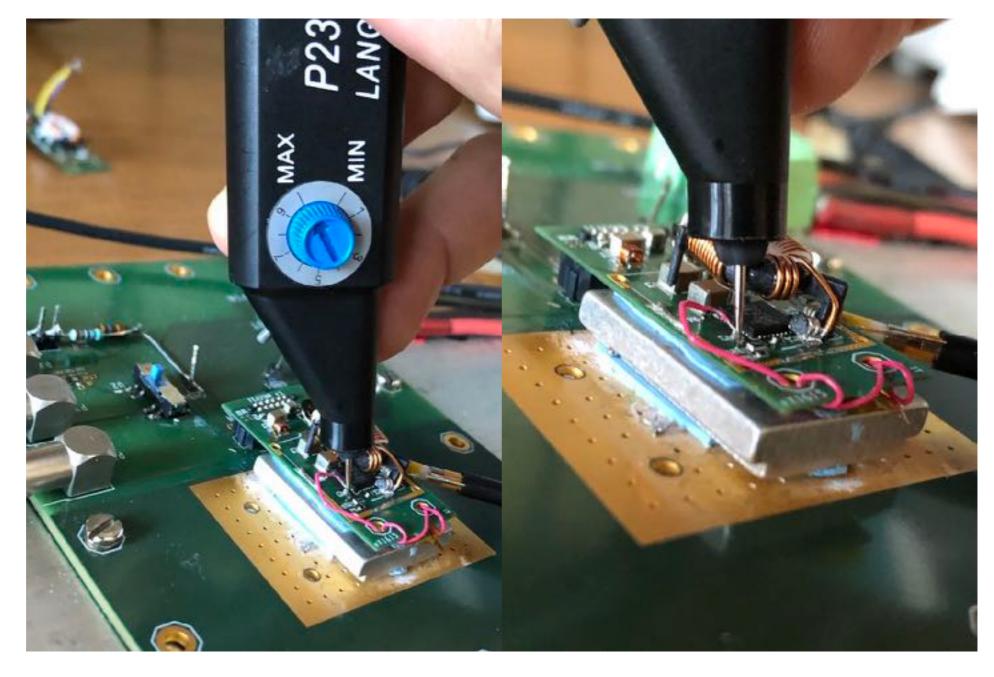

Capacitive high-frequency coupler used on the input bus line

AC-observation of the effect of a 3kV (!) pulse with 50ns duration on Vin and V33Dr. The peak is several V above the DC (V33Dr reaches 8V)!

#### **EM noise? Environmental conditions?**

High-frequency, large power RF noise injection could produce damage with different signature

Led by F. Szoncso and D. Valuch

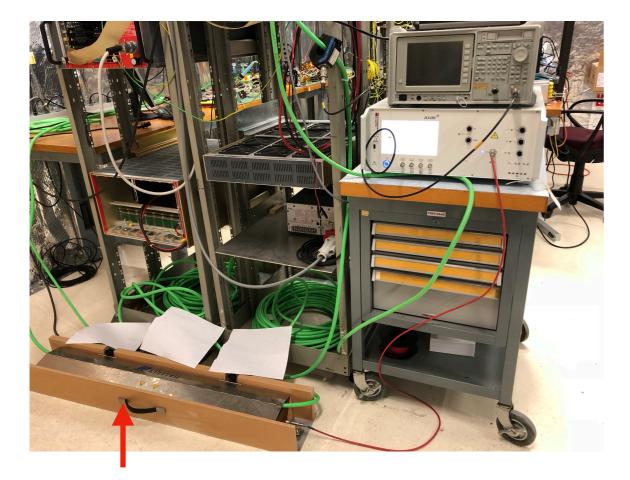

High frequency (GHz) and high power transient pulses are injected via an antenna in a special chamber in CERN Prévessin. At very large power, the ASIC can be damaged but the signature is different than in samples failing in CMS. Coupling is through the long enable line.

#### **EM noise? Environmental conditions?**

Stress tests with an ESD gun (1.2kV pulses) could produce somewhat similar damage - but the energy injected needs to be really large

An ESD gun is used to inject a discharge to the different pins of the FEAST2 package. To produce any damage, a visible spark has to be produced.

#### **Radiation in ASIC?**

SEE Heavy Ion irradiation on samples pre-exposed to X-rays, Protons and Neutrons did not show any sign of damage

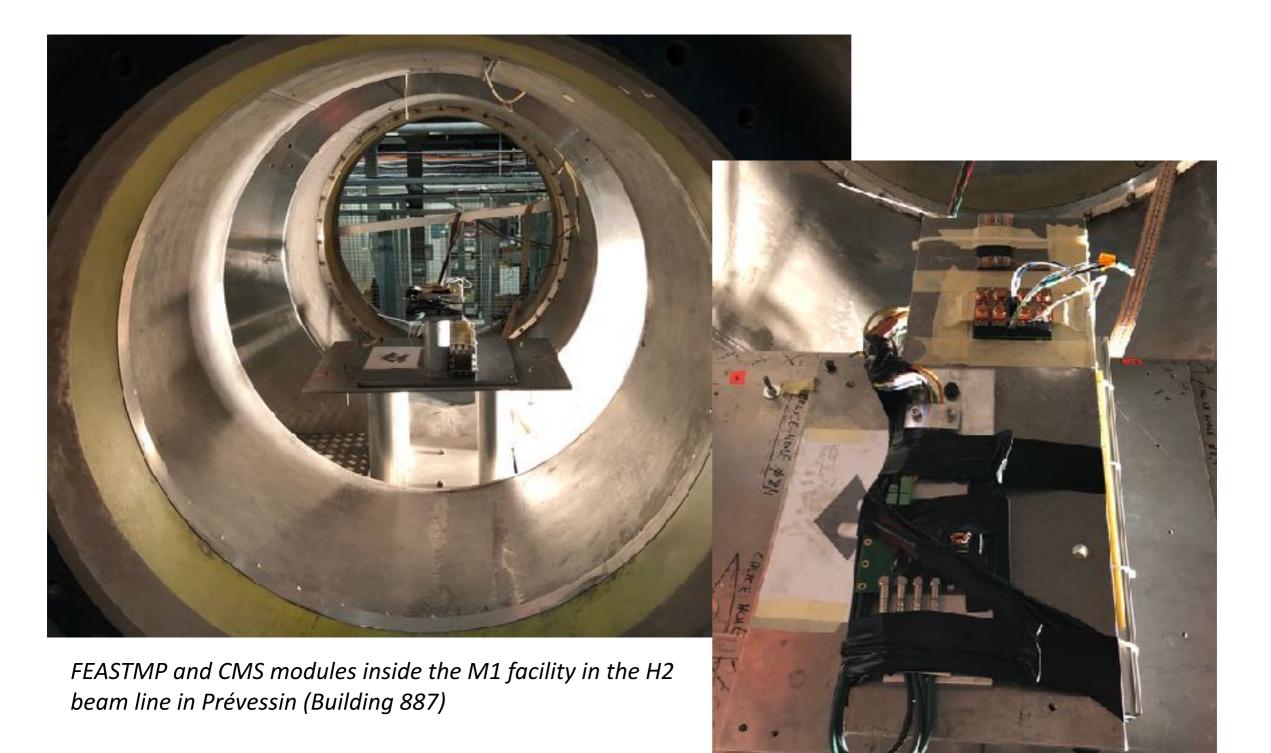

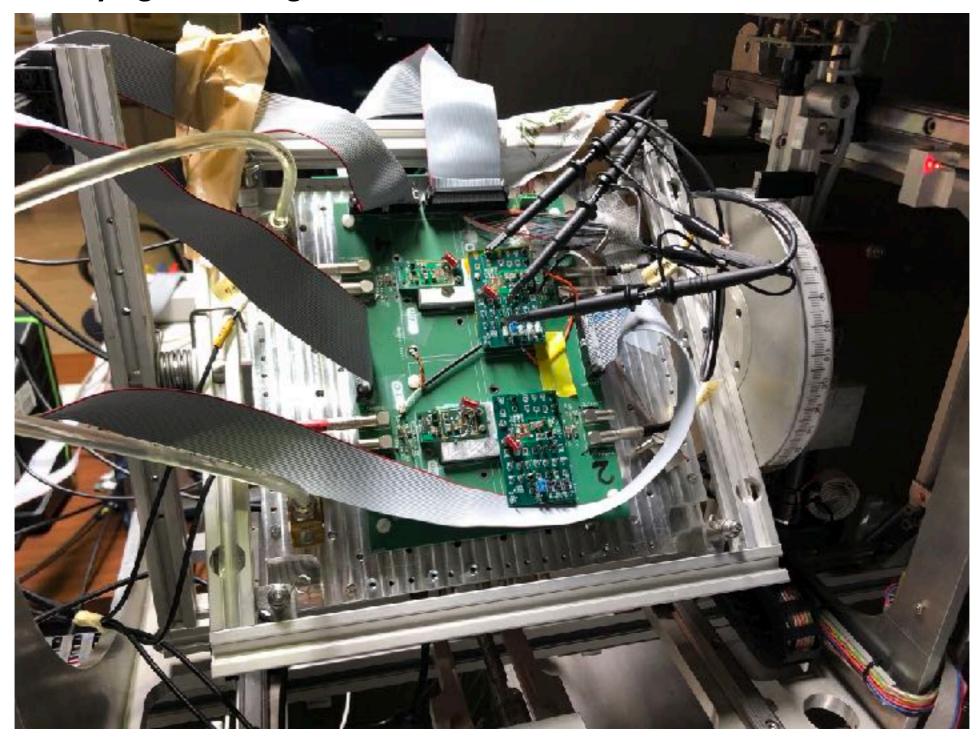

4 modules prepared on a motherboard are placed inside the irradiation chamber where they will be exposed to a Heavy Ion beam. The FEAST2 chips were previously irradiated with X-rays, 230MeV protons or neutrons from a reactor.

#### **Radiation in ASIC? Environmental conditions?**

Exposure of 32 FEAST2 in the CMS Castor Table was meant to reproduce some of the environmental conditions (proximity to the beam line, EM environment, radiation environment)

32 sample DCDC modules, both FEASTMP and CMS modules, are exposed and constantly monitored in the CMS Castor Table during the 2018 run.

**Radiation in ASIC?**

**Environmental conditions?**

EM noise?

Two irradiation runs at the CERN IRRAD facility were instrumental in understanding the origin of the damage

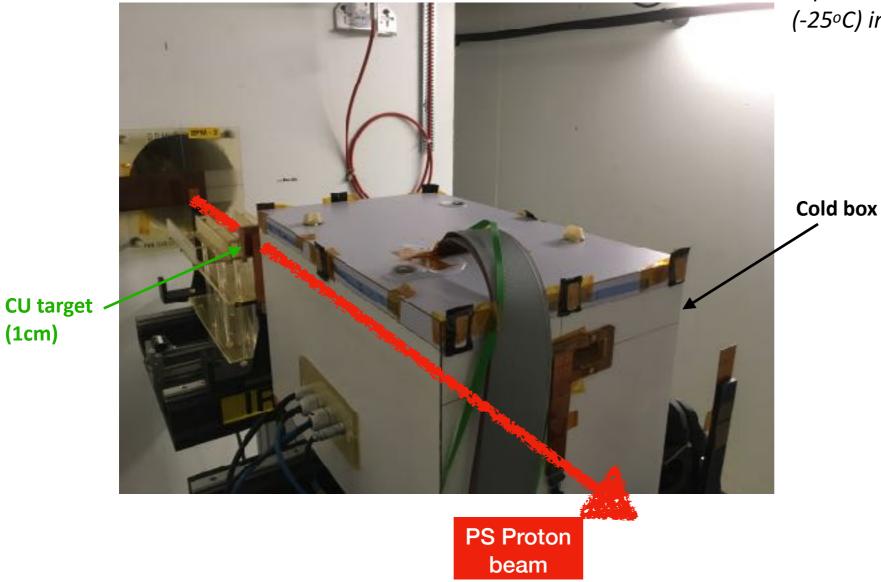

#### Exposure of 32 FEAST2 at -25°C at the CERN IRRAD facility

The facility run in a purposely modified configuration to expose the converters in a mixed field: MANY THANKS to the IRRAD TEAM!

32 samples, both FEASTMP and CMS modules, are exposed and constantly monitored in a cold box (-25°C) in the CERN IRRAD facility (May 2018).

32 modules inside the cold box

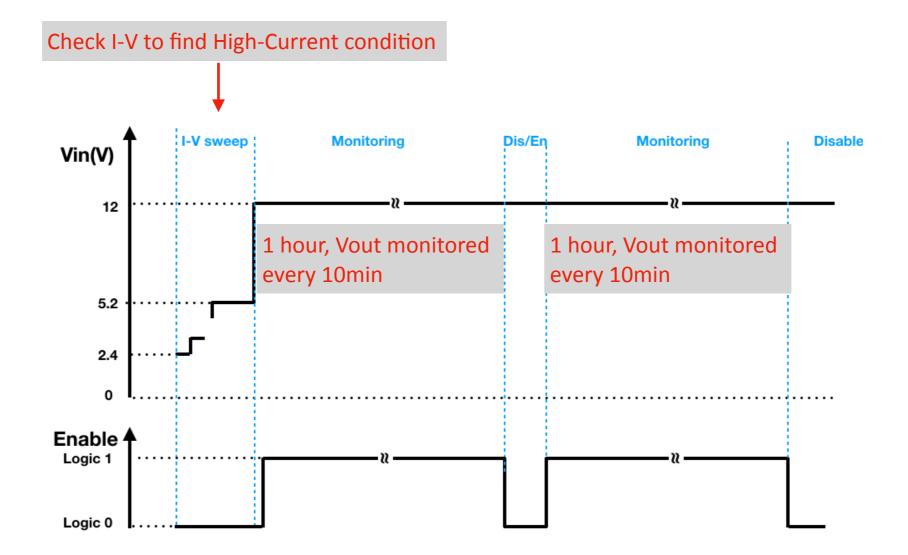

#### A specific bias and control sequence was used during the exposure

The full sequence lasts about 2 hours, with 97% of the time in "monitoring"

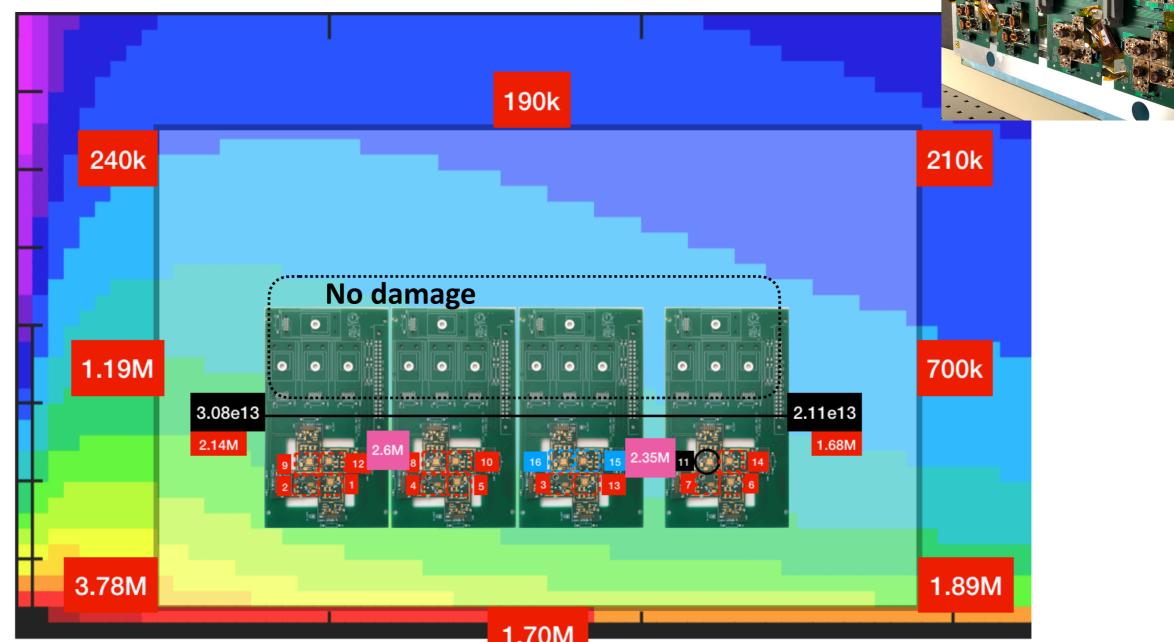

#### The results powerfully revealed some important correlation:

#### - Between the damage and the integrated flux

- The first damage occurs after 9 days, then several samples per day

- Only samples closer to the beam are damaged

- Samples are damaged also after the end of the exposure

- Between the occurrence of the damage and the disable-enable sequence

- Also true for the "High-Current"

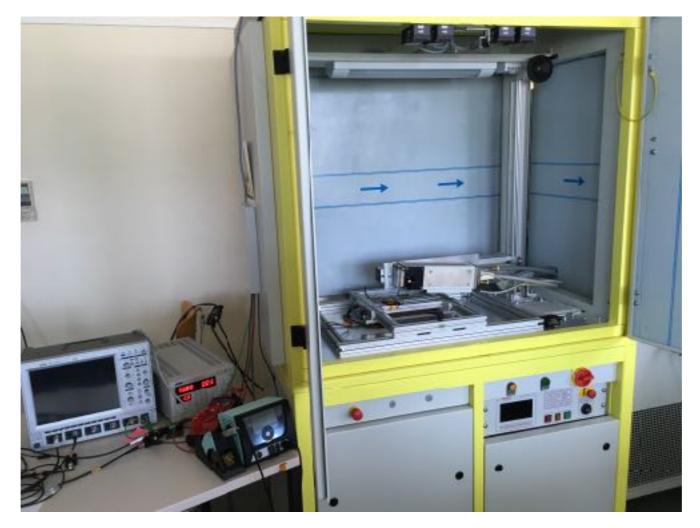

**Red** = High-Current damage occurred during exposure **Blue** = High-Current damage occurred after exposure **Black** = failure X-ray irradiation using the same enable/disable cycle as in IRRAD, and monitoring the current under UVLO thresholds, it was eventually possible to produce the same damage!

Now we had a tool to study the mechanism in detail!

X-ray machine of the EP-ESE group

### The crime reconstruction

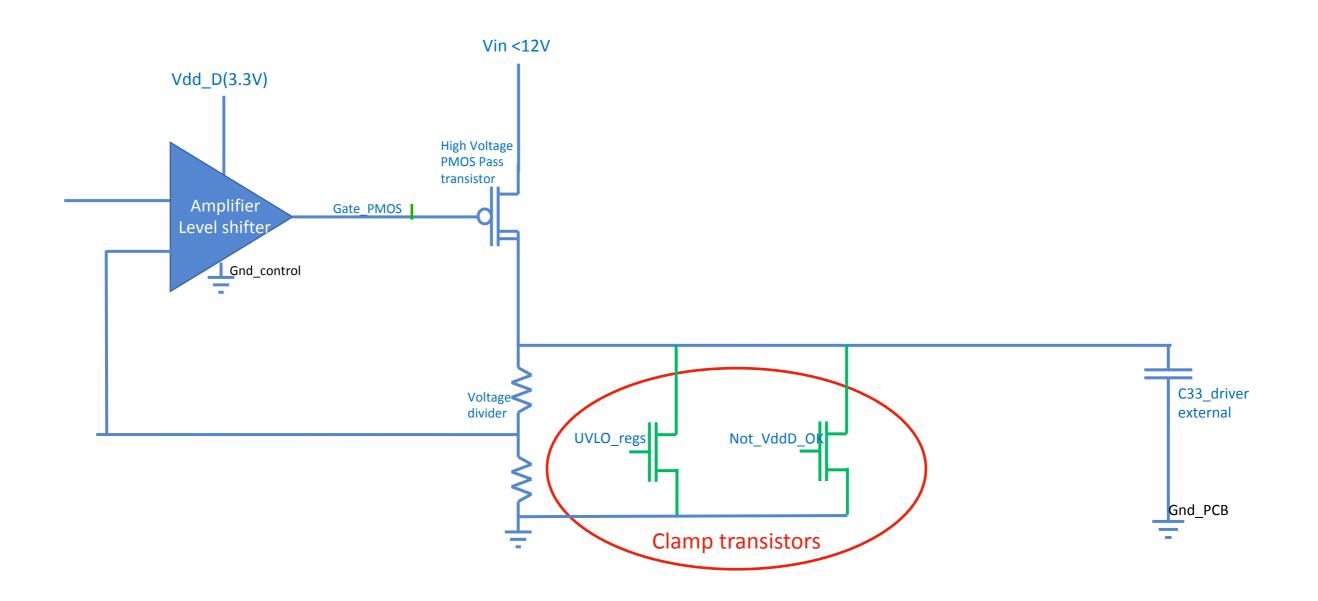

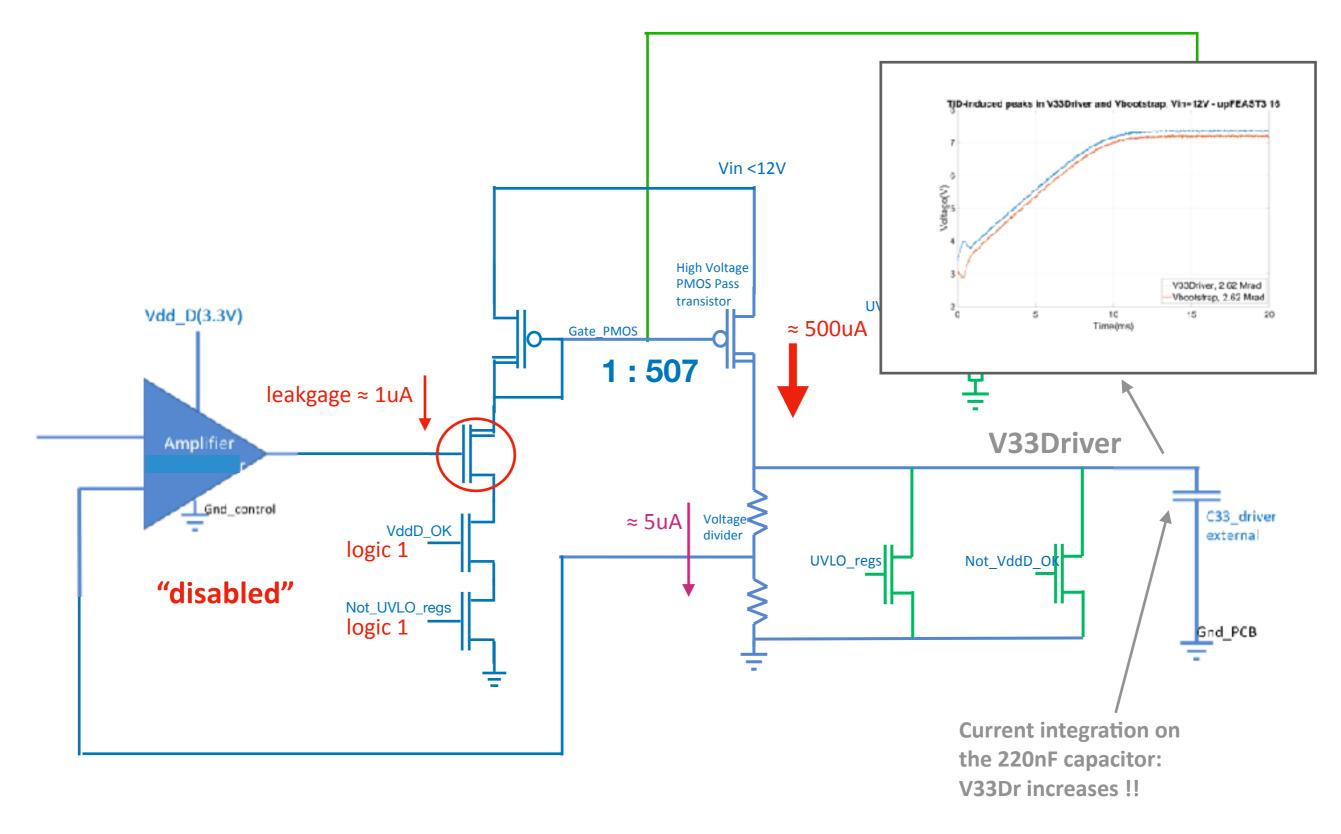

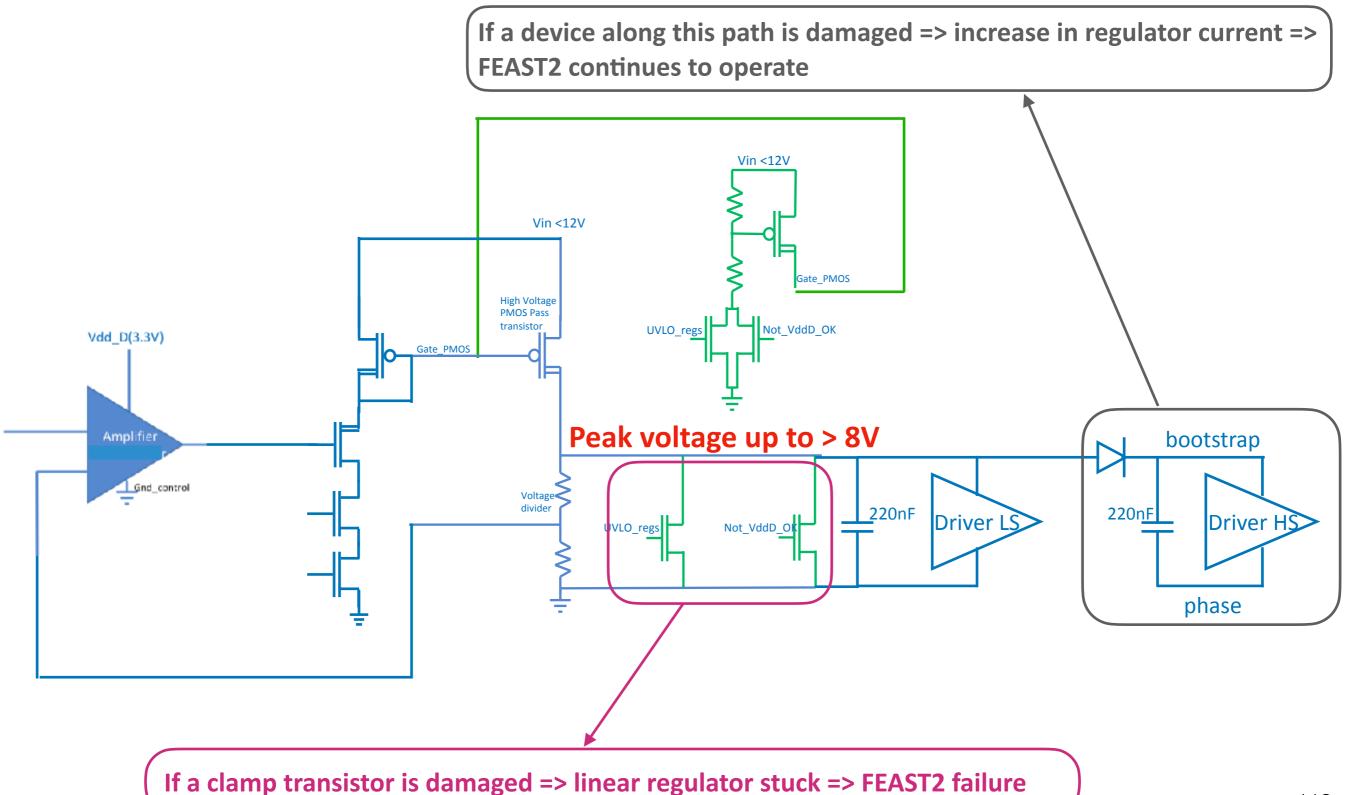

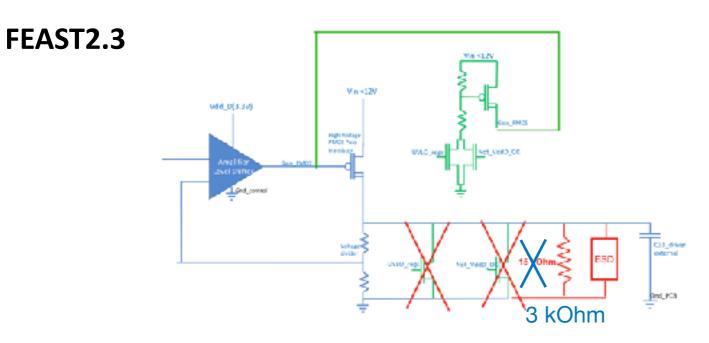

The problem is localised in the linear regulator (V33Dr) that provides the required current to the drivers of the power transistors (HS and LS)

In the presence of a large TID-induced leakage in the nLDMOS, consequences appear ONLY when FEAST2 is disabled (no load for the V33Dr regulator)

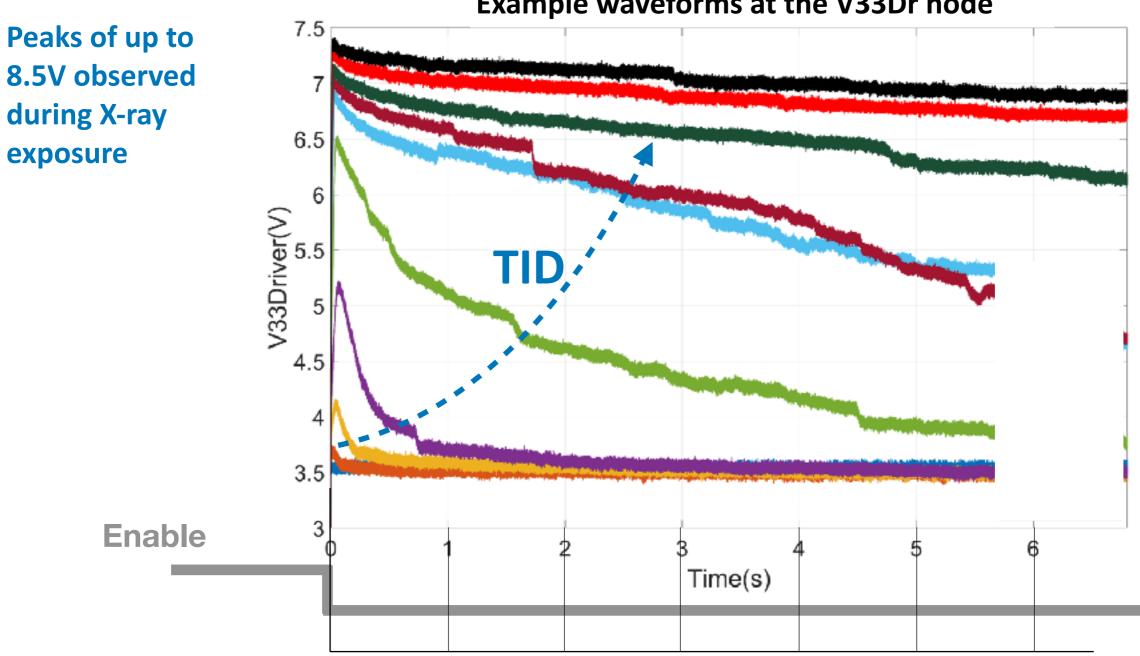

We observed a "voltage peak" on the V33Dr node when FEAST2 is disabled during X-ray exposures. The voltage peak increases with TID

Example waveforms at the V33Dr node

The voltage at the V33Dr node goes well beyond the nominal maximum of 3.3V+10%. This voltage stress might end up damaging a device. We have observed 2 damage mechanisms, and Failure Analysis with emission microscopy and OBIRCH have confirmed the current paths.

## A graphical representation of the narrative

## The perpetrator

2 easy to implement patches were used to rapidly fix the problem. Then a permanent solution was implemented in a new version of the circuit.

Present default version for all modules

# Thoughts inspired by this FEAST2 crisis

## This is a very complex system

- Assembly of different sub-systems

- Unique "prototype"

- Tested in the real environment only

#### We are not NASA in the 1970s...

### Some reasons to be grateful for our luck

- The designers of the failing component were still around, and at CERN

- The problem happened to a detector that is amongst the easier to open

- Once understood, patches and fixes were easy to implement

- The problem appeared in 2017 and not in HL-LHC trackers

Personally I'm always ready to learn, although I do not always like being taught

W. Churchill